产品概述:

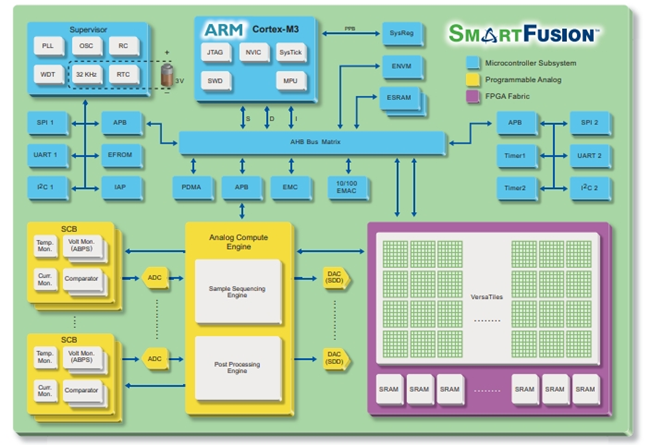

A2F200M3F-1CS288I SmartFusion片上系统(SoC)FPGA是唯一集成FPGA结构、Arm Cortex -M3处理器和可编程模拟电路的器件,提供完全定制和ip保护的优势,同时仍然易于使用。

SmartFusion SoC FPGA基于专有闪存工艺,非常适合需要真正的SoC解决方案的硬件和嵌入式设计人员,这种解决方案比传统的固定功能微控制器具有更大的灵活性,而没有传统FPGA上软处理器内核的过高成本。

特征:

微控制器系统(MSS):

100 MHz 的 32 位 ARM® Cortex™-M3,零等待状态存储器实现 1.25 DMIPS/MHz 吞吐量

存储器保护单元(MPU)

单周期乘法,硬件除法

JTAG 调试(四线),串行线调试(SWD–双线)和单线浏览器(SWV)接口

嵌入式 Flash 存储器(eNVM),64K 字节~512K 字节

嵌入式高速 SRAM(eSRAM),16K 字节~64K 字节,含 2 个物理块,2 个不同主机可同时访问它

片上存储器的带宽最高可达 16 Gbps

带 RMII 接口的 10/100 以太网 MAC

可编程的外部存储器控制器

异步存储器

NOR Flash,SRAM,PSRAM

同步 SRAM

两个 I2C 外设

两个 16550 UART

两个 SPI 外设

两个 32 位定时器

32 位看门狗定时器

8 通道 DMA 控制器

1.5 MHz~20 MHz 主振荡器

电池供电的、带实时计数器(RTC)的 32 KHz 低功率振荡器

精度为 1%的 100 MHz 嵌入式 RC 振荡器

带 4 个输出相位的嵌入式 PLL

高性能FPGA:

采用基于 Flash 的、130nm、7 层金属的 CMOS 工艺

非易失,断电时保留程序

350 MHz 系统性能

嵌入式 SRAM 与 FIFO

SRAM block 的长宽比可调节

可选用×1,×2,×4,×9 与×18 组合

真实双端口 SRAM(×18 组合除外)

可编程的嵌入式 FIFO 控制逻辑

通过 JTAG 采用 128 位高级加密标准(AES)解密技术实现安全 ISP

采用 FlashLock 技术保护 FPGA 内容

5 个时钟调节电路(CCC)模块,每个模块最多可带 2 个集成模拟 PLL

相移、分频/倍频、延时等均可配置

频率:输入为 1.5~350 MHz,输出为 0.75~350 MHz

可编程模拟前端(AFE):

最多可包含 3 个 12 位 SAR ADC

12 位模式时的速率为 500 Ksps

8 位和 10 位模式时的速率为 600 Ksps

2.56V 内部参考电压或者外部参考电压

每个 ADC 包含一个一级 Sigma-Delta(Σ- )DAC

12 位 500 Ksps 更新速率

每个器件最多可包含 5 个新的高性能模拟信号调节模块(SCB),每个模块包括:

2 个高电压双极电压监控器(4 个输入的电压为±2.5V~-11.5/+14V),精度为 1%

高增益电流监控器,差分增益=50,共模电压高达 14V

温度监控器(12 位模式时的分辨率=1/4℃;准确温度范围是-55℃~150℃)

多达 10 个高速比较器(tpd = 50ns)