SWCS044H-NOVEMBER 2009-REVISED JULY 2011

# 8-CHANNEL HIGH\_QUALITY LOW-POWER AUDIO CODEC FOR PORTABLE APPLICATIONS

Check for Samples: TWL6040

## FEATURES

- Four audio digital-to-analog (DAC) channels

- Stereo capless headphone drivers:

- Up to 104-dB DR

- Power tune for performance/power consumption tradeoff

- Stereo 8 Ω, 1.5 W per channel speaker drivers

- **Differential earpiece driver**

- Stereo line-out

- Two audio analog-to-digital (ADC) channels:

- 96-dBA SNR

- Four audio inputs:

- Three differential microphone inputs

- Stereo line-in/FM input

- Two vibrator/haptics feedback channels:

- Differential H-bridge drivers

- Two low-noise analog microphone bias outputs

- Two digital microphone bias outputs

- Analog low-power loop from line-in to headphone/speaker outputs

- Dual phase-locked loops (PLLs) for flexible clock support:

- 32-kHz sleep clock input for system low-power playback mode

- 12-/19.2-/26-/38.4-MHz system clock input

- Accessory plug/unplug detection, accessory button press detection

- Integrated power supplies:

- \_ Negative charge pump for capless headphone driver

- Two low dropout voltage regulators (LDOs) for high power supply rejection ratio (PSRR)

- I<sup>2</sup>C control

- Thermal protection:

- Host interrupt

- **Power supplies:**

- Analog: 2.1 V

- Digital I/O: 1.8 V

- Battery 2.3 to 5.5 V

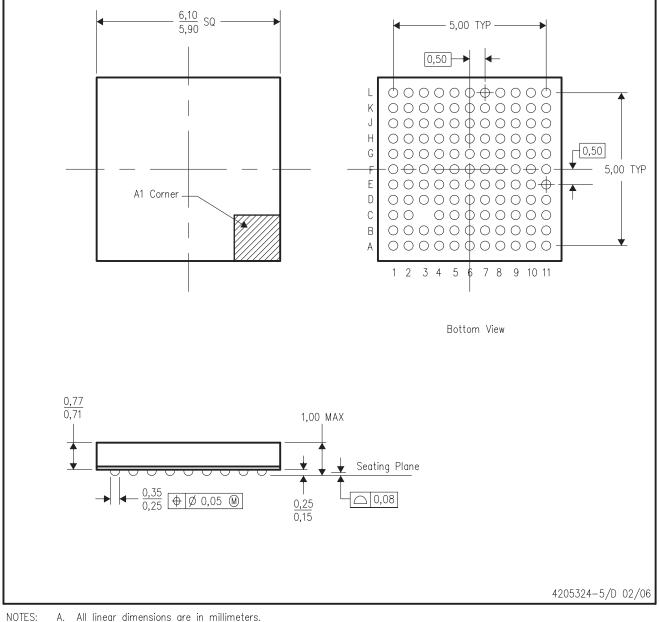

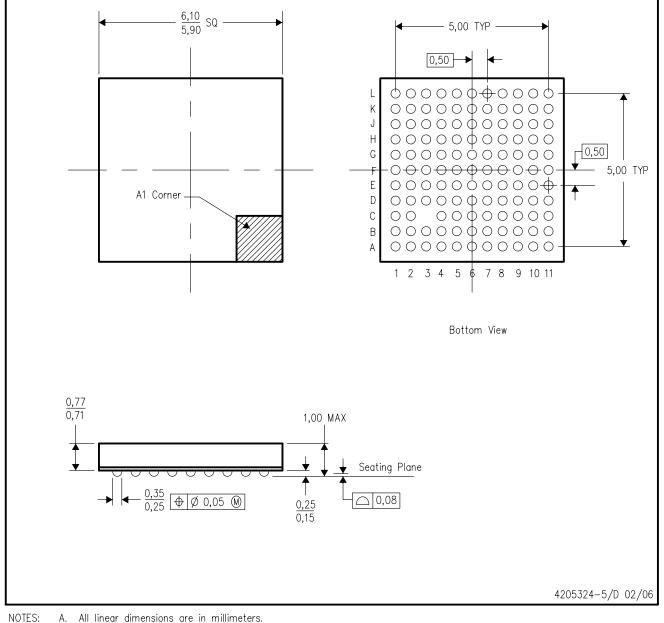

- Package 6-mm × 6-mm 120-pin PBGA

## APPLICATIONS

- Mobile and smart phones

- MP3 players

- Handheld devices

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. OMAP4 is a trademark of Texas Instruments.

www.ti.com

## DESCRIPTION

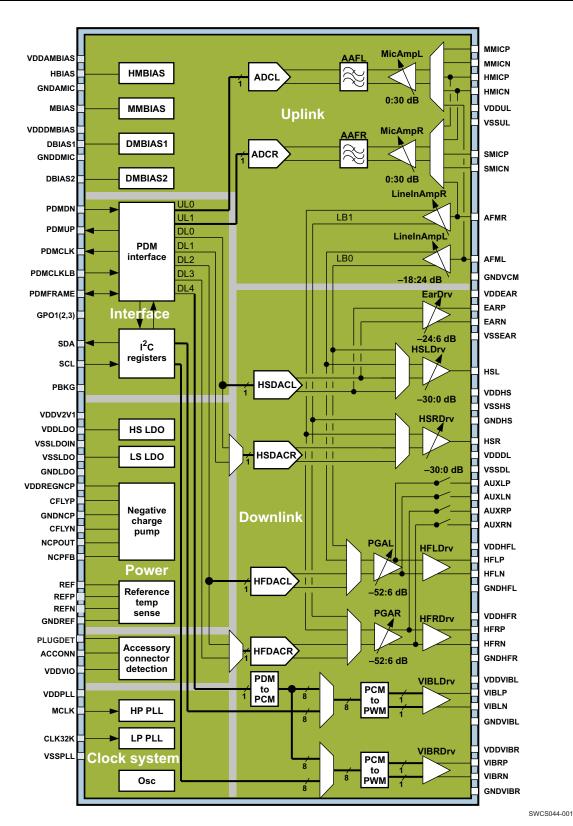

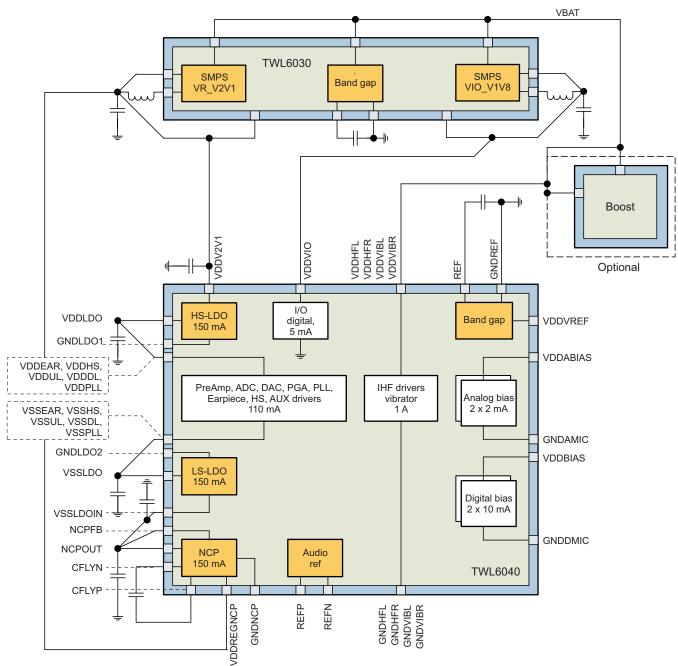

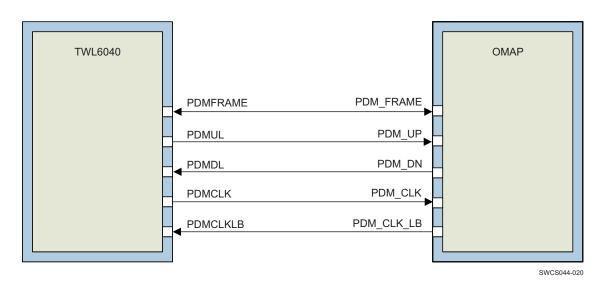

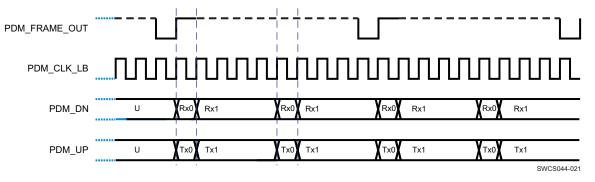

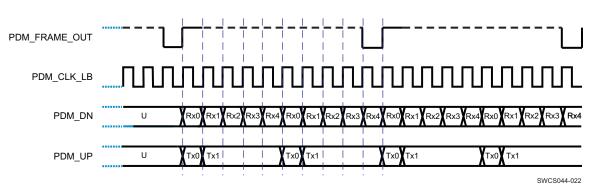

The TWL6040 device is an audio coder/decoder (codec) with a high level of integration providing analog audio codec functions for portable applications, as shown in Figure 1. It contains multiple audio analog inputs and outputs, as well as microphone biases and accessory detection. It is connected to the OMAP4<sup>™</sup> host processor through a proprietary PDM interface for audio data communication enabling partitioning with optimized power consumption and performance. Multichannel audio data is multiplexed to a single wire for downlink (PDML) and uplink (PDMUL).

The OMAP4 device provides the TWL6040 device with five PDM audio-input channels (DL0–DL4). Channels DL0–DL3 are connected to four parallel DAC channels multiplexed to stereo headphone (HSL, HSR), stereo speaker (HFL, HFR), and earpiece (EAR) or stereo line outputs (AUXL, AUXR).

The stereo headphone path has a low-power (LP) mode operating from a 32-kHz sleep clock to enable more than 100 hours of MP3 playback time. Very-high dynamic range of 104 dBA is achieved when using the system clock input and DAC path high-performance (HP) mode. Class-AB headphone drivers provide a 1-V<sub>rms</sub> output and are ground centered for capless connection to headphone, thus enabling system size and cost reduction. The earpiece driver is a differential class-AB driver with 2 V<sub>rms</sub> capability to a typical 32- $\Omega$  load or 1.4 V<sub>rms</sub> to a typical 16- $\Omega$  load.

Stereo speaker path has filterless class-D outputs with 1.5-W capability per channel. For output power maximization supply connection to an external boost is supported. Speaker drivers also support also hearing aid coil loads. For vibrator and haptic feedback support, the TWL6040 has two PWM channels with independent input signals from DL4 or inter-integrated circuit (I<sup>2</sup>C<sup>™</sup>).

Vibrator drivers are differential H-bridge outputs, enabling fast acceleration and deceleration of vibrator motor. An external driver for a hearing aid coil or a piezo speaker requiring high voltage can be connected to line outputs.

The TWL6040 supports three differential microphone inputs (MMIC, HMIC, SMIC) and a stereo line-input (AFML, AFMR) multiplexed to two parallel ADCs. The PDM output from the ADCs is transmitted to the OMAP4 processor through UL0 and UL1. AFML, AFMR inputs can also be looped to analog outputs (LB0, LB1).

Two LDOs provide a voltage of 2.1 V to bias analog microphones (MBIAS and HBIAS). The maximum output current is 2 mA for each analog bias, allowing up to two microphones on one bias. Two LDOs provide a voltage of 1.8 V/1.85 V to bias digital microphones (DBIAS1 and DBIAS2). One bias generator can bias up several digital microphones at the same time, with a total maximum output current of 10 mA.

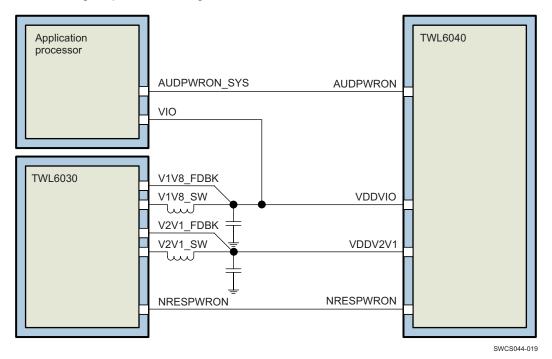

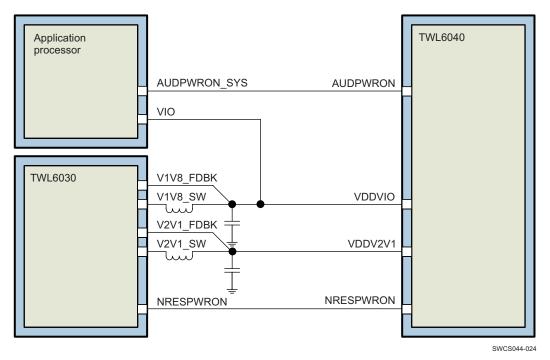

The TWL6040 has an integrated negative charge pump (NCP) and two LDOs (HS LDO and LS LDO) for high PSRR. The only external supply needed is 2.1 V, which is available from the 2.1-V DC-DC of the TWL6030 power management IC (PMIC) in the OMAP4 system. By powering audio from low-noise 2.1-V DC-DC of low power consumption, high dynamic range and high output swing at headset output are achieved. All other supply inputs can be directly connected to battery or system 1.8-V I/O.

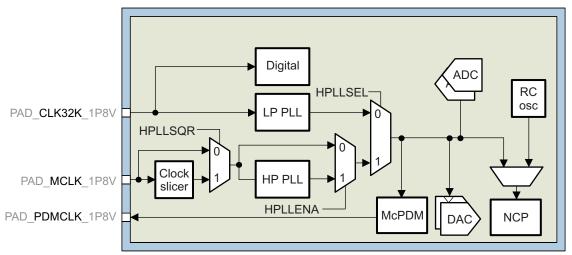

Two integrated PLLs enable operatation from a 12/19.2/26/38.4-MHz system clock (MCLK) or, in LP playback mode, from a 32-kHz sleep clock (CLK32K). The frequency plan is based on a 48-kS/s audio data rate for all channels, and host processor uses sample-rate converters to interface with different sample rates (for example, 44.1 kHz). In the specific case of low-power audio playback, the 44.1-kS/s and 48-kS/s rates are supported by the TWL6040. Transitions between sample rates or input clocks are seamless.

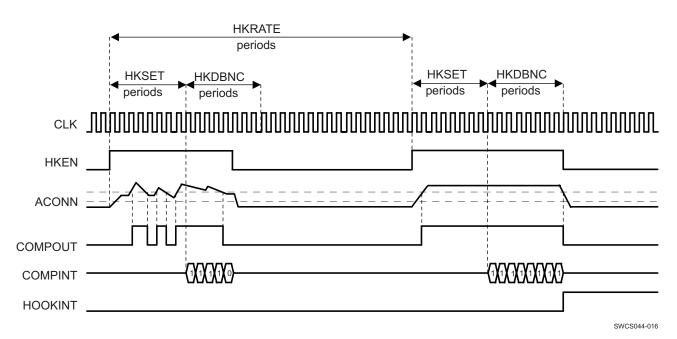

Accessory plug and unplug detections are supported (PLUGDET). Some headsets have a manual switch for submitting send/end signal to the terminal through the microphone input pin. This feature is supported by a periodic accessory button press detection to minimize current consumption in sleep mode. Detection cycle properties can be programmed according to system requirements.

Figure 1 shows a simplified block diagram of the device.

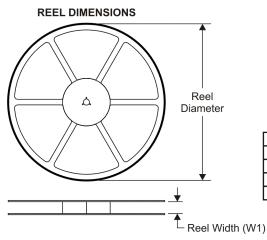

### Table 1. ORDERING INFORMATION

| PART NUMBER | PACKAGE          | ORDERING       | MEDIUM |

|-------------|------------------|----------------|--------|

| TWL6040     | 6-mm × 6-mm PBGA | TWL6040A2ZQZ/R | Reel   |

www.ti.com

Figure 1. Simplified Block Diagram

| Table 2. Terminal Functions |      |         |                    |                                                |  |  |  |

|-----------------------------|------|---------|--------------------|------------------------------------------------|--|--|--|

| NAME                        | BALL | TYPE    | I/O <sup>(1)</sup> | DESCRIPTION                                    |  |  |  |

| MCLK                        | K7   | Digital | I                  | System clock                                   |  |  |  |

| CLK32K                      | H7   | Digital | I                  | Real-time clock (RTC)                          |  |  |  |

| AUDPWRON                    | D8   | Digital | I                  | Power-up signal                                |  |  |  |

| NRESPWRON                   | J9   | Digital | I                  | Power-up reset                                 |  |  |  |

| NAUDINT                     | E8   | Digital | 0                  | Interrupt                                      |  |  |  |

| SDA                         | H6   | Digital | I/O                | I <sup>2</sup> C serial interface data         |  |  |  |

| SCL                         | G6   | Digital | I                  | I <sup>2</sup> C serial interface clock        |  |  |  |

| PDMCLKLB                    | K8   | Digital | I                  | PDM loopback clock                             |  |  |  |

| PDMCLK                      | L10  | Digital | 0                  | PDM reference clock                            |  |  |  |

| PDMFRAME                    | H8   | Digital | I/O                | PDM frame                                      |  |  |  |

| PDMDN                       | K9   | Digital | I                  | PDM downlink audio data                        |  |  |  |

| PDMUP                       | L8   | Digital | 0                  | PDM uplink audio data                          |  |  |  |

| Uplink Channel              |      |         | -                  |                                                |  |  |  |

| HBIAS                       | J3   | Power   | 0                  | Headset microphone bias supply                 |  |  |  |

| MBIAS                       | K3   | Power   | 0                  | Main analog microphone bias supply             |  |  |  |

| DBIAS1                      | J5   | Power   | 0                  | Digital microphone 1 <sup>st</sup> bias supply |  |  |  |

| DBIAS2                      | L4   | Power   | 0                  | Digital microphone 2 <sup>nd</sup> bias supply |  |  |  |

| MMICP                       | K1   | Analog  | I                  | Main microphone (+)                            |  |  |  |

| MMICN                       | J2   | Analog  | I                  | Main microphone (-)                            |  |  |  |

| SMICP                       | J4   | Analog  | I                  | Submicrophone (+)                              |  |  |  |

| SMICN                       | H4   | Analog  | I                  | Submicrophone (-)                              |  |  |  |

| HMICP                       | H1   | Analog  | I                  | Headset microphone (+)                         |  |  |  |

| HMICN                       | H2   | Analog  | I                  | Headset microphone (-)                         |  |  |  |

| AFML                        | F1   | Analog  | I                  | Auxiliary or FM radio left input               |  |  |  |

| AFMR                        | F2   | Analog  | I                  | Auxiliary or FM radio right input              |  |  |  |

| Downlink Channel            | L.   |         |                    |                                                |  |  |  |

| EARP                        | B10  | Analog  | 0                  | Earphone output (+)                            |  |  |  |

| EARN                        | C11  | Analog  | 0                  | Earphone output (-)                            |  |  |  |

| HSL                         | J11  | Analog  | 0                  | Headset left output                            |  |  |  |

| HSR                         | K11  | Analog  | 0                  | Headset right output                           |  |  |  |

| AUXLP                       | G3   | Analog  | 0                  | Auxiliary predriver left output (+)            |  |  |  |

| AUXLN                       | F3   | Analog  | 0                  | Auxiliary predriver left output (-)            |  |  |  |

| AUXRP                       | G4   | Analog  | 0                  | Auxiliary predriver right output (+)           |  |  |  |

| AUXRN                       | F4   | Analog  | 0                  | Auxiliary predriver right output (-)           |  |  |  |

| HFLP1                       | A4   | Analog  | 0                  | Hands-free left output (+)                     |  |  |  |

| HFLP2                       | B4   | Analog  | 0                  | Hands-free left output (+)                     |  |  |  |

| HFLN1                       | A5   | Analog  | 0                  | Hands-free left output (-)                     |  |  |  |

| HFLN2                       | B5   | Analog  | 0                  | Hands-free left output (-)                     |  |  |  |

| HFRP1                       | B9   | Analog  | 0                  | Hands-free right output (+)                    |  |  |  |

| HFRP2                       | A9   | Analog  | 0                  | Hands-free right output (+)                    |  |  |  |

| HFRN1                       | B8   | Analog  | 0                  | Hands-free right output (-)                    |  |  |  |

| HFRN2                       | A8   | Analog  | 0                  | Hands-free right output (-)                    |  |  |  |

| VIBLP                       | C1   | Analog  | 0                  | Vibrator left output (+)                       |  |  |  |

| VIBLN                       | D3   | Analog  | 0                  | Vibrator left output (-)                       |  |  |  |

| VIBRP                       | A2   | Analog  | 0                  | Vibrator right output (+)                      |  |  |  |

| VIBRN                       | B1   | Analog  | 0                  | Vibrator right output (-)                      |  |  |  |

(1) I = Input; O = Output

## TEXAS INSTRUMENTS

SWCS044H-NOVEMBER 2009-REVISED JULY 2011

www.ti.com

## Table 2. Terminal Functions (continued)

| Table 2. Terminal Functions (continued) |      |        |                    |                                         |  |  |  |  |  |

|-----------------------------------------|------|--------|--------------------|-----------------------------------------|--|--|--|--|--|

| NAME                                    | BALL | TYPE   | I/O <sup>(1)</sup> | DESCRIPTION                             |  |  |  |  |  |

| Positive Supplies                       |      | 1      |                    |                                         |  |  |  |  |  |

| VDDVREF                                 | H5   | Power  | I                  | Reference system supply                 |  |  |  |  |  |

| VDDLDO                                  | D1   | Power  | 0                  | High-side LDO output                    |  |  |  |  |  |

| VDDEAR                                  | B11  | Power  | I                  | Earphone positive supply                |  |  |  |  |  |

| VDDHS                                   | J10  | Power  | I                  | Headset positive supply                 |  |  |  |  |  |

| VDDUL                                   | G2   | Power  | I                  | Uplink codec positive supply            |  |  |  |  |  |

| VDDDL                                   | E9   | Power  | I                  | Downlink codec positive supply          |  |  |  |  |  |

| VDDPLL                                  | J7   | Power  | I                  | PLL positive supply                     |  |  |  |  |  |

| VDDHFL1                                 | A3   | Power  | I                  | Hands-free left positive supply         |  |  |  |  |  |

| VDDHFL2                                 | A6   | Power  | I                  | Hands-free left positive supply         |  |  |  |  |  |

| VDDHFR1                                 | A7   | Power  | I                  | Hands-free right positive supply        |  |  |  |  |  |

| VDDHFR2                                 | A10  | Power  | I                  | Hands-free right positive supply        |  |  |  |  |  |

| VDDVIBL                                 | C2   | Power  | I                  | Vibrator positive supply                |  |  |  |  |  |

| VDDVIBR                                 | B2   | Power  | I                  | Vibrator positive supply                |  |  |  |  |  |

| VDDAMBIAS                               | L2   | Power  | I                  | Analog microphone bias supply           |  |  |  |  |  |

| VDDDMBIAS                               | K4   | Power  | I                  | Digital microphone bias supply          |  |  |  |  |  |

| VDDREGNCP                               | H11  | Power  | I                  | Negative charge pump positive supply    |  |  |  |  |  |

| VDDV2V1                                 | E2   | Power  | I                  | Preregulated main positive supply       |  |  |  |  |  |

| VDDVIO                                  | L9   | Power  | I                  | Interface I/O supply                    |  |  |  |  |  |

| Negative Supplies                       |      |        |                    |                                         |  |  |  |  |  |

| CFLYN                                   | F11  | Power  | 0                  | Flying capacitor negative terminal      |  |  |  |  |  |

| CFLYP                                   | G11  | Power  | 0                  | Flying capacitor positive terminal      |  |  |  |  |  |

| NCPOUT1                                 | E10  | Power  | 0                  | Negative charge pump output             |  |  |  |  |  |

| NCPOUT2                                 | E11  | Power  | 0                  | Negative charge pump output             |  |  |  |  |  |

| NCPFB                                   | G9   | Power  | I                  | Negative SMPS feedback                  |  |  |  |  |  |

| VSSLDOIN                                | D11  | Power  | I                  | Low-side LDO input supply               |  |  |  |  |  |

| VSSLDO                                  | D10  | Power  | 0                  | Low-side LDO output                     |  |  |  |  |  |

| VSSEAR                                  | C10  | Power  | I                  | Earphone negative supply                |  |  |  |  |  |

| VSSHS                                   | H10  | Power  | I                  | Headset negative supply                 |  |  |  |  |  |

| VSSUL                                   | G1   | Power  | I                  | Uplink negative supply                  |  |  |  |  |  |

| VSSDL                                   | F9   | Power  | I                  | Downlink negative supply                |  |  |  |  |  |

| VSSPLL                                  | L7   | Power  | I                  | PLL negative supply                     |  |  |  |  |  |

| Ground                                  | L.   |        | - IL               |                                         |  |  |  |  |  |

| GN DREF                                 | K5   | Ground | I                  | Bandgap reference ground                |  |  |  |  |  |

| GNDHS                                   | H9   | Ground | I                  | Headset sense input                     |  |  |  |  |  |

| GNDAMIC                                 | H3   | Ground | I                  | Analog microphone ground                |  |  |  |  |  |

| GNDDMIC                                 | L3   | Ground | I                  | Digital microphone and accessory ground |  |  |  |  |  |

| GNDLDO1                                 | E3   | Ground | I                  | HS and LS LDO ground                    |  |  |  |  |  |

| GNDLDO2                                 | D9   | Ground | I                  | HS and LS LDO ground                    |  |  |  |  |  |

| GNDVCM                                  | J1   | Ground | I                  | Codec ground                            |  |  |  |  |  |

| GNDNCP1                                 | F10  | Ground | I                  | Negative charge pump ground             |  |  |  |  |  |

| GNDNCP2                                 | G10  | Ground | I                  | Negative charge pump ground             |  |  |  |  |  |

| GNDHFL1                                 | C5   | Ground | I                  | Hands-free left driver ground           |  |  |  |  |  |

| GNDHFL2                                 | C4   | Ground | I                  | Hands-free left driver ground           |  |  |  |  |  |

| GNDHFL3                                 | C6   | Ground | I                  | Hands-free left driver ground           |  |  |  |  |  |

| GNDHFR1                                 | C7   | Ground |                    | Hands-free right driver ground          |  |  |  |  |  |

Copyright © 2009–2011, Texas Instruments Incorporated

# TWL6040

### SWCS044H-NOVEMBER 2009-REVISED JULY 2011

## Table 2. Terminal Functions (continued)

| NAME          | BALL | TYPE    | I/O <sup>(1)</sup> | DESCRIPTION                    |  |  |  |  |  |  |

|---------------|------|---------|--------------------|--------------------------------|--|--|--|--|--|--|

| GNDHFR2       | C8   | Ground  | I                  | Hands-free right driver ground |  |  |  |  |  |  |

| GNDHFR3       | C9   | Ground  | I                  | Hands-free right driver ground |  |  |  |  |  |  |

| GNDDIG        | J6   | Ground  | I                  | Digital ground                 |  |  |  |  |  |  |

| GNDVIBR       | B3   | Ground  | I                  | Vibrator driver ground         |  |  |  |  |  |  |

| GNDVIBL       | D2   | Ground  | I                  | Vibrator driver ground         |  |  |  |  |  |  |

| GNDIO         | J8   | Ground  | I                  | General-purpose I/O ground     |  |  |  |  |  |  |

| PBKG1         | F5   | Ground  | I                  | Substrate package ground       |  |  |  |  |  |  |

| PBKG2         | F6   | Ground  | I                  | Substrate package ground       |  |  |  |  |  |  |

| PBKG3         | F7   | Ground  | I                  | Substrate package ground       |  |  |  |  |  |  |

| PBKG4         | E4   | Ground  | I                  | Substrate package ground       |  |  |  |  |  |  |

| PBKG5         | K10  | Ground  | I                  | Substrate package ground       |  |  |  |  |  |  |

| Miscallaneous |      |         |                    |                                |  |  |  |  |  |  |

| REF           | L5   | Analog  | I/O                | Bandgap reference              |  |  |  |  |  |  |

| REFP          | K6   | Analog  | I/O                | Positive converter reference   |  |  |  |  |  |  |

| REFN          | L6   | Analog  | I/O                | Negative converter reference   |  |  |  |  |  |  |

| ATEST         | K2   | Analog  | 0                  | Analog test pin                |  |  |  |  |  |  |

| GPO1          | D4   | Digital | 0                  | General-purpose output 1       |  |  |  |  |  |  |

| GPO2          | B6   | Digital | 0                  | General-purpose output 2       |  |  |  |  |  |  |

| GPO3          | B7   | Digital | 0                  | General-purpose output 3       |  |  |  |  |  |  |

| DTEST1        | A1   | Digital | I                  | Digital test pin 1             |  |  |  |  |  |  |

| DTEST2        | L1   | Digital | I                  | Digital test pin 2             |  |  |  |  |  |  |

| DTEST3        | A11  | Digital | I                  | Digital test pin 3             |  |  |  |  |  |  |

| PROG          | L11  | Digital | I                  | EEPROM programming pin         |  |  |  |  |  |  |

| ACCONN        | E1   | Analog  | I/O                | Accessory connector pin        |  |  |  |  |  |  |

| PLUGDET       | G5   | Analog  | l                  | Accessory plug detection pin   |  |  |  |  |  |  |

|               |      | 1       | 1                  |                                |  |  |  |  |  |  |

TEXAS INSTRUMENTS

www.ti.com

SWCS044H-NOVEMBER 2009-REVISED JULY 2011

TWL6040

| r | 1          | 2             | 3           | 4                 | 5           | 6          | 7          | 8            | 9                 | 10         | 11                |

|---|------------|---------------|-------------|-------------------|-------------|------------|------------|--------------|-------------------|------------|-------------------|

| А | DTEST1     | VIB<br>RP     | VDD<br>HFL  | HFLP              | HFLN        | VDD<br>HFL | VDD<br>HFR | HFRN         | HFRP              | VDD<br>HFR | DTEST3            |

| В | VIB<br>RN  | VDD<br>VIBR   | GND<br>VIBR | HFLP              | HFLN        | GPO2       | GPO3       | HFRN         | HFRP              | EARP       | VDD<br>EAR        |

| С | VIB<br>LP  | VDD<br>VIBL   |             | GND<br>HFL        | GND<br>HFL  | GND<br>HFL | GND<br>HFR | GND<br>HFR   | GND<br>HFR        | VSS<br>EAR | EARN              |

| D | VDD<br>LDO | GND<br>VIBL   | VIB<br>LN   | GPO1              |             |            |            | AUDP<br>WRON | GND<br>LDO2       | VSS<br>LDO | VSS<br>LDOIN      |

| Е | ACC<br>ONN | VDD<br>V2V1   | GND<br>LDO1 | PBKG              |             |            |            | NAUD<br>INT  | VDD<br>DL         | NCP<br>OUT | NCP<br>OUT        |

| F | AFML       | AFMR          | AUX<br>LN   | AUX<br>RN         | PBKG        | PBKG       | PBKG       |              | VSS<br>DL         | GND<br>NCP | CFLYN             |

| G | VSS<br>UL  | VDD<br>UL     | AUX<br>LP   | AUX<br>RP         | PLUG<br>DET | SCL        |            |              | NCP<br>FB         | GND<br>NCP | CFLYP             |

| н | HMICP      | HMICN         | GND<br>AMIC | SMICN             | VDD<br>VREF | SDA        | CLK<br>32K | PDM<br>FRAME | GND<br>HS         | VSS<br>HS  | VDD<br>REG<br>NCP |

| J | GND<br>VCM | MMICN         | HBIAS       | SMICP             | DBIAS1      | GND<br>DIG | VDD<br>PLL | GND<br>IO    | NRES<br>PWR<br>ON | VDD<br>HS  | HSL               |

| К | MMICP      | ATEST         | MBIAS       | VDD<br>DM<br>BIAS | GND<br>REF  | REFP       | MCLK       | PDM<br>CLKLB | PDM<br>DN         | PBKG       | HSR               |

| L | DTEST2     | VDDA<br>MBIAS | GND<br>DMIC | DBIAS2            | REF         | REFN       | VSS<br>PLL | PDM<br>UP    | VDD<br>VIO        | PDM<br>CLK | PROG              |

| l |            |               |             |                   |             |            |            |              |                   |            | SWCS044-002       |

Figure 2. Pin Assignment (Top View)

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted)

Stresses beyond those listed below may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated below are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| PARAMETER                                | TEST CONDITIONS          | MIN  | ТҮР | MAX | UNIT |

|------------------------------------------|--------------------------|------|-----|-----|------|

|                                          | DC                       | -0.3 |     | 5.5 | V    |

| Supply voltage                           | AC, 1000 spikes of 10 ms | -0.3 |     | 6   | V    |

|                                          | duration over 7 years    |      |     |     |      |

| Ambient operating temperature            |                          | -30  |     | 85  | °C   |

| Storage temperature                      |                          | -55  |     | 150 | °C   |

| Electrostatic discharge protection (HBM) |                          | 2    |     |     | kV   |

| Electrostatic discharge protection (CDM) |                          | 500  |     |     | V    |

## THERMAL CHARACTERISTICS<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

| PACKAGE         | POWER (W) | R <sub>⊝JA</sub> (°C/W) | R <sub>⊝JB</sub> (°C/W) | R <sub>⊝JC</sub> (°C/W) | BOARD TYPE |

|-----------------|-----------|-------------------------|-------------------------|-------------------------|------------|

| PBGA, 6mm x 6mm | 0.4       | 34                      | 22                      | 8                       | 2S2P       |

(1) NOTE: The maximum power, 0.4 W, is at 85°C ambient temperature.

(a)  $R_{\theta JA}$  (Theta-JA) = Thermal Resistance Junction-to-Ambient, °C/W

(b)  $R_{\theta JB}$  (Theta-JB) = Thermal Resistance Junction-to-Board, °C/W (c)  $R_{\theta JC}$  (Theta-JC) = Thermal Resistance Junction-to-Case, °C/W

## **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted)

| PARAMETER                            | MIN   | NOM   | MAX   | UNIT |

|--------------------------------------|-------|-------|-------|------|

| Supply voltage                       |       |       |       |      |

| VBAT                                 | 2.3   | 3.7   | 5.5   | V    |

| V2V1                                 | 2.039 | 2.127 | 2.205 | V    |

| VIO                                  | 1.747 | 1.823 | 1.89  |      |

| Operating junction temperature range | -30   |       | 125   | °C   |

| Operating ambient temperature range  | -30   |       | 85    | C    |

## **CURRENT CONSUMPTION**

Over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                                                                                              | MIN | NOM  | MAX  | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Power-off mode: only battery supply present, other supplies pulled down. From VBAT (2.3–5.5 V)                                                         |     | 0.54 | 4.4  |      |

| Deep-sleep mode: 1.8 V I/O present, other regulated supplies pulled down, plug detection enabled, other modules disabled. From VBAT (3.8 V)            |     | 1.4  | 15.3 |      |

| Sleep mode: all supplies present. No accessory connected, plug detection enabled, other modules disabled. From VBAT (3.6 V)                            |     | 2.4  | 17.6 | μA   |

| Sleep mode: all supplies present. Accessory connected, accessory unplug and button press detections enabled, other modules disabled. From VBAT (3.6 V) |     | 15.2 | 40.5 |      |

www.ti.com

## UPLINK MICROPHONE CHANNEL

Over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                 | TEST CONDITIONS                                                                  | MIN   | TYP  | MAX  | UNIT    |  |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------|------|---------|--|

| Single-ended or differential input swing 0 dBFs (Th                       |                                                                                  |       |      | 2    | Vpp     |  |

| Single-ended or differential input slew rate                              |                                                                                  |       |      | 1    | V/µs    |  |

| Programmable preattenuation                                               |                                                                                  | -6    |      | 0    | dB      |  |

| • .                                                                       |                                                                                  | -0    |      | 30   | dB      |  |

| Programmable preamplifier gain                                            |                                                                                  | 0     | 6    | 30   |         |  |

| Programmable preamplifier gain step size                                  |                                                                                  |       | 6    | 0.5  | dB      |  |

| Absolute gain accuracy                                                    | Gain = Min                                                                       | -0.5  |      | 0.5  | dB      |  |

| Relative gain accuracy                                                    | Gain = Min to Max referenced to gain = Min                                       | -0.5  |      | 0.5  | dB      |  |

| Gain step size accuracy                                                   | Referenced to step = Typ                                                         | -0.25 |      | 0.25 | dB      |  |

| Gain variation with frequency                                             | f = 20-20  kHz,<br>relative to $f = 1 \text{ kHz}$<br>without external capacitor | -0.5  |      | 0.5  | dB      |  |

| Single-ended input resistance                                             |                                                                                  | 160   | 200  | 240  | kΩ      |  |

|                                                                           | 0 dBFs                                                                           |       | -42  | -40  |         |  |

|                                                                           | –10 dBFs                                                                         |       | -72  | -70  |         |  |

| Total harmonic distortion in 20–20 kHz bandwidth<br>Gain = Min, f = 1 kHz | –20 dBFs                                                                         |       | -67  | -65  | dB(A)   |  |

|                                                                           | –40 dBFs                                                                         |       | -47  | -45  |         |  |

|                                                                           | –60 dBFs                                                                         |       | -27  | -25  |         |  |

| Input referred idle channel noise (including                              | 20 Hz to 8 kHz, gain = 6 dB                                                      |       | 10.9 | 14.8 |         |  |

| microphone bias and typical microphone biasing                            | 20 Hz to 8 kHz, gain = 24 dB                                                     |       | 2.5  | 3.3  |         |  |

| circuitry)                                                                | 20 Hz to 20 kHz, gain = 6 dB                                                     |       | 13.6 | 18.6 |         |  |

|                                                                           | 20 Hz to 20 kHz, gain = 12 dB                                                    |       | 6.7  | 9.6  | µVrms(A |  |

|                                                                           | 20 Hz to 20 kHz, gain = 18 dB                                                    |       | 4.1  | 5.6  |         |  |

|                                                                           | 20 Hz to 20 kHz, gain = 24 or 30 dB                                              |       | 3    | 4    |         |  |

| Signal-to-noise ratio                                                     | 20 Hz to 8 kHz, gain = 6 dB                                                      | 92    | 98   |      |         |  |

|                                                                           | 20 Hz to 8 kHz, gain = 24 dB                                                     | 86    | 92   |      |         |  |

|                                                                           | 20 Hz to 20 kHz, gain = $6 \text{ dB}$                                           | 90    | 96   |      | dB(A)   |  |

|                                                                           | 20 Hz to 20 kHz, gain = 24 or 30 dB                                              | 84    | 90   |      |         |  |

| Power supply rejection from VBAT                                          | Gain = Min                                                                       |       |      |      |         |  |

|                                                                           | VBAT > 2.3 V, f < 1 kHz                                                          | 74    |      |      |         |  |

|                                                                           | VBAT > 2.3 V, f < 8 kHz                                                          | 56    |      |      |         |  |

|                                                                           | VBAT > 2.3 V, f < 20 kHz                                                         | 48    |      |      | dB(A)   |  |

|                                                                           | VBAT > 2.5 V, f < 1 kHz                                                          | 80    |      |      | GD(//)  |  |

|                                                                           | VBAT > 2.5 V, f < 8 kHz                                                          | 62    |      |      |         |  |

|                                                                           | VBAT > 2.5 V, f < 20 kHz                                                         | 54    |      |      |         |  |

| Antialias attenuation at Fs                                               | 6-dB gain                                                                        | 15    | 22   |      |         |  |

|                                                                           | 24-dB gain                                                                       | 30    | 40   |      | dB      |  |

| Interchannel crosstalk and separation                                     | Input at 1 kHz and –20 dBFs                                                      | 50    | 40   | 60   | dB      |  |

| interentarinter erosstalik antu separationi                               | Preamplifier Gain = 18 dB                                                        |       |      | 00   | υD      |  |

| Input-to-output leakage                                                   | Input at 1 kHz and 0 dBFs                                                        |       | -80  | -74  | dB      |  |

| Common mode rejection                                                     | 20 Hz to 20 kHz                                                                  |       | 60   | 45   | dB      |  |

| Delay                                                                     | MicAmp input to McPDM output                                                     |       |      | 4    | μs      |  |

| Total uplink current from VBAT = 3.6 V                                    | Mono                                                                             |       | 3    | 4.6  | r       |  |

| (with analog microphone load)                                             | Stereo                                                                           |       | 5.9  | 7.8  | mA      |  |

## ANALOG MICROPHONE BIAS

Over operating free-air temperature range (unless otherwise noted)

| ANALOG MICROPHONE BIAS                          |                                      |      |      |      |           |  |  |  |

|-------------------------------------------------|--------------------------------------|------|------|------|-----------|--|--|--|

| PARAMETER                                       | TEST CONDITIONS                      | MIN  | TYP  | MAX  | UNIT      |  |  |  |

| Positive supply voltage (VDDAMBIAS)             | At the pad                           | 2.3  | 3.6  | 5    | V         |  |  |  |

| Negative supply voltage (GNDAMIC)               | At the pad                           |      | 0    |      | V         |  |  |  |

| Output voltage (V <sub>OUT</sub> )              | Normal mode                          | 2.06 | 2.1  | 2.14 | V         |  |  |  |

|                                                 | Sleep mode                           | 2.06 | 2.1  | 2.2  | V         |  |  |  |

| Output current (I <sub>L</sub> )                | Normal mode                          | 0    | 0.6  | 2    | mA        |  |  |  |

|                                                 | Sleep mode                           | 0    |      | 0.2  | mA        |  |  |  |

| Integrated noise                                | f = 20 Hz to 8 kHz                   |      | 1.65 | 2.3  | µVrms (P) |  |  |  |

|                                                 | f = 20 Hz to 8 kHz                   |      | 3    | 4    | µVrms (A) |  |  |  |

|                                                 | f = 20 Hz to 20 kHz                  |      | 3.5  | 5    | µVrms (A) |  |  |  |

| Power supply rejection from VDDAMBIAS           | $I_L = 0$ to Max, $C_f = Min$ to Max |      |      |      |           |  |  |  |

|                                                 | VDDAMBIAS > 2.3 V, f < 1 kHz         | 74   |      |      |           |  |  |  |

|                                                 | VDDAMBIAS > 2.3 V, f < 8 kHz         | 56   |      |      | dB(A)     |  |  |  |

|                                                 | VDDAMBIAS > 2.3 V, f < 20 kHz        | 48   |      |      |           |  |  |  |

|                                                 | VDDAMBIAS > 2.5 V, f < 1 kHz         | 80   | 100  |      |           |  |  |  |

|                                                 | VDDAMBIAS > 2.5 V, f < 8 kHz         | 62   | 80   |      |           |  |  |  |

|                                                 | VDDAMBIAS > 2.5 V, f < 20 kHz        | 54   |      |      |           |  |  |  |

| Load transient                                  | 80% I <sub>L</sub> Max in 1 μs       |      |      | 30   | mV        |  |  |  |

| Startup time                                    | V <sub>OUT</sub> at 90%              |      |      | 200  | μs        |  |  |  |

| Short-circuit current limit                     | Output shorted to ground             | 3    | 6    | 10   | mA        |  |  |  |

| Output impedance in power-down mode             | dc, with respect to GND              | 3    |      |      |           |  |  |  |

|                                                 | VOUT from 0 to 2.1 V                 |      |      |      | MΩ        |  |  |  |

|                                                 | V2V1 enabled                         |      |      |      |           |  |  |  |

| Pulldown                                        | DC, with respect to GND              |      |      | 200  | Ω         |  |  |  |

| Quiescent current                               | Normal mode, $I_L = 0-Max$           |      | 200  | 300  |           |  |  |  |

|                                                 | Sleep mode, $I_L = 0-Max/10$         |      | 10   | 20   | μA        |  |  |  |

| Parasitic board capacitor Cp                    |                                      |      |      | 200  | pF        |  |  |  |

| External filter resistor value R <sub>f</sub>   |                                      | 185  | 200  | 215  | Ω         |  |  |  |

| External filter capacitor value C <sub>f</sub>  | Ceramic capacitor                    | 0    | 220  | 250  | nF        |  |  |  |

| External capacitor ESR                          | f = 100 kHz                          |      |      | 6    | Ω         |  |  |  |

| Biasing resistance R <sub>b</sub>               |                                      | 2.09 | 2.2  | 2.31 | kΩ        |  |  |  |

| Microphone equivalent resistance R <sub>m</sub> |                                      | 1    | 3    | 6    | kΩ        |  |  |  |

www.ti.com

## **DIGITAL MICROPHONE BIAS**

Over operating free-air temperature range (unless otherwise noted)

| DIGITAL MICROPHONE BIAS               |                                         |      |      |      |       |  |  |

|---------------------------------------|-----------------------------------------|------|------|------|-------|--|--|

| PARAMETER                             | TEST CONDITIONS                         | MIN  | TYP  | MAX  | UNIT  |  |  |

| Positive supply voltage (VDDDMBIAS)   | At the pad                              | 2.3  | 3.6  | 5    | V     |  |  |

| Negative supply voltage (GNDDMIC)     | At the pad                              |      | 0    |      | V     |  |  |

| Output dc voltage (V <sub>OUT</sub> ) | Normal mode, $I_L = 0$ to Max           | 1.75 | 1.8  | 1.85 |       |  |  |

|                                       | Sleep mode, $I_L = 0$ to Max/10         | 1.8  | 1.85 | 1.9  | V     |  |  |

| Output current (I <sub>L</sub> )      |                                         | 0    |      | 10   | mA    |  |  |

| Power supply rejection from VDDDMBIAS | $I_L = 200 \ \mu A$ to Max, normal mode |      |      |      |       |  |  |

|                                       | V <sub>OUT</sub> = 1.8 V, f < 20 kHz    | 40   |      |      | dB(A) |  |  |

| Load transient                        | 80% I <sub>L</sub> Max in 1 µs          |      |      | 30   | mV    |  |  |

| Output impedance in power-down mode   | DC, with respect to GND                 | 1    |      |      | MΩ    |  |  |

| Startup time                          |                                         |      |      | 600  | μs    |  |  |

| Short-circuit current limit           | Output shorted to ground                | 20   | 30   | 40   | mA    |  |  |

| Quiescent current                     | Normal mode                             |      | 20   | 30   |       |  |  |

|                                       | Sleep mode                              |      | 7    | 10   | μA    |  |  |

| External capacitor value              |                                         | 0.9  | 2.2  | 3.3  | μF    |  |  |

| External capacitor ESR                | f < 100 kHz                             |      |      | 0.6  | Ω     |  |  |

|                                       | 1 MHz < f < 10 MHz                      |      |      | 0.02 | Ω     |  |  |

## ANALOG LOOP, LINE-IN TO HEADPHONE OUTPUT

Over operating free-air temperature range (unless otherwise noted)

| ANALOG LOOP, LINE-IN TO HEADPHONE OUTPUT                             |                                                      |     |     |     |       |  |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------------|-----|-----|-----|-------|--|--|--|--|

| PARAMETER                                                            | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT  |  |  |  |  |

| Programmable gain range in line-in amplifier                         |                                                      |     | 42  |     | dB    |  |  |  |  |

| Programmable gain in line-in amplifier                               |                                                      | -18 |     | 24  | dB    |  |  |  |  |

| Programmable gain step size                                          |                                                      |     | 6   |     | dB    |  |  |  |  |

| Single-ended input resistance                                        |                                                      | 40  | 50  | 60  | kΩ    |  |  |  |  |

| Maximum input voltage (0 dBFs)                                       | For single-ended input                               |     |     | 2   | Vpp   |  |  |  |  |

| Total analog loop SNR output                                         | Gain = 0 dB, 0.5 V <sub>rms</sub> signal             |     | 90  |     | dB(A) |  |  |  |  |

| Total analog loop THDN at FS                                         | LineG = 6 dB, HSDrvG = 0 dB,<br>output = 1 $V_{rms}$ |     | -66 |     | dB    |  |  |  |  |

| Total stereo analog loop path quiescent current<br>85% DC 3.8-V Vbat | From VBAT = 3.8 V                                    |     | 2.5 | 3.5 | mA    |  |  |  |  |

TEXAS INSTRUMENTS

www.ti.com

## DOWNLINK (DAC) CHANNEL TO HEADPHONE OUTPUT

Over operating free-air temperature range (unless otherwise noted)

| DOWNLINK (DAC) CHANNEL TO HEADPHON                                                         |                                                                     |       | T)/D  | MAN  |                       |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------|------|-----------------------|--|

| PARAMETER                                                                                  | TEST CONDITIONS                                                     | MIN   | TYP   | MAX  | UNIT                  |  |

| Speaker load resistance (RL)                                                               |                                                                     | 16    | 32    |      | Ω                     |  |

| Single-ended output swing 0 dBFs (THD > 40 dB, $-4$ dB analog gain in HP mode and $-2$ -dB | at the ball R <sub>L</sub> + R <sub>f</sub> = 32 + 15 = 47 $\Omega$ | 1     |       |      | Vrme                  |  |

| gain in LP mode)                                                                           | at the load R <sub>L</sub> + R <sub>f</sub> = 32 + 15 = 47 $\Omega$ | 0.7   |       |      | Vrms                  |  |

| Programmable gain range                                                                    |                                                                     | -30   |       | 0    | dB                    |  |

| Programmable gain step size                                                                |                                                                     |       | 2     |      | dB                    |  |

| Absolute gain accuracy                                                                     | Gain = Max                                                          | -0.5  |       | 0.5  | dB                    |  |

| Relative gain accuracy                                                                     | Relative to gain = Max                                              | -0.5  |       | 0.5  | dB                    |  |

| Gain step size accuracy                                                                    |                                                                     | -0.25 |       | 0.25 | dB                    |  |

| Gain variation with frequency                                                              | f = 20 Hz to 20 kHz, gain = Min to<br>Max                           | -1.1  | -0.85 | -0.6 | dB                    |  |

|                                                                                            | relative to 1 kHz at the ball                                       |       |       |      |                       |  |

| Idle channel noise                                                                         | LP mode, at the ball                                                |       | 10    | 14   | $u (max o (\Lambda))$ |  |

| Gain = Max                                                                                 | HP mode, at the ball                                                |       | 6     | 9    | µVrms(A)              |  |

| Dynamic range                                                                              | HP mode                                                             |       | 104   |      | dB(A)                 |  |

| –60-dBFs output with –4-dB analog gain                                                     |                                                                     |       |       |      |                       |  |

| Dynamic range                                                                              | LP mode                                                             | 100   | 103   |      |                       |  |

| –60-dBFs output with –30-dB analog gain                                                    | HP mode                                                             | 105   | 108   |      | dB(A)                 |  |

| Signal-to-noise ratio                                                                      | –1-dBFs output, LP mode                                             | 94    | 97    |      |                       |  |

|                                                                                            | –1-dBFs output, HP mode                                             | 98    | 101   |      |                       |  |

|                                                                                            | –10-dBFs output, LP mode                                            | 86    | 89    |      | dB(A)                 |  |

|                                                                                            | –10-dBFs output, HP mode                                            | 90    | 93    |      |                       |  |

| Total harmonic distortion in 20 Hz–20 kHz                                                  | 0 dBFs                                                              |       |       | -40  |                       |  |

| bandwidth                                                                                  | –10 dBFs                                                            |       |       | -70  |                       |  |

| (sine-wave @1 kHz, gain = Max)                                                             | –20 dBFs                                                            |       |       | -56  | dB(A)                 |  |

|                                                                                            | –40 dBFs                                                            |       |       | -36  |                       |  |

|                                                                                            | –60 dBFs                                                            |       |       | –16  |                       |  |

| THD+N                                                                                      | $R_L = 32 \Omega$ , Pload = 20 mW (-2.5 dBFS)                       |       | 0.012 | 0.1  | %                     |  |

| Power supply rejection from VBAT                                                           | Gain = Max, 217 Hz TDMA pulse<br>noise                              | 80    | 100   |      | dB(A)                 |  |

| HS reference GNDHS noise rejection                                                         | f = 1 kHz, 10 mV <sub>rms</sub> amplitude                           | 40    |       |      | ~ /                   |  |

| Group delay                                                                                |                                                                     |       |       | 7.1  | μs                    |  |

| Offset                                                                                     | From stand-alone IC                                                 | -16   |       | 16   |                       |  |

|                                                                                            | After system compensation                                           | -2    |       | 2    | mV                    |  |

| L/R gain mismatch                                                                          | at 0 dBFs, 1 kHz                                                    | -0.5  |       | 0.5  | dB                    |  |

| L/R phase mismatch                                                                         | at 0 dBFs, 1 kHz                                                    | -10   |       | 10   | degrees               |  |

| L/R cross-talk                                                                             | at 0 dBFs, 1 kHz                                                    |       |       | -60  | dB                    |  |

| Output impedance                                                                           | Driver and pulldown disabled                                        | 1     |       |      | MΩ                    |  |

| Average playback current from VBAT                                                         | LP mode                                                             |       | 5.3   | 7    |                       |  |

|                                                                                            | HP mode                                                             |       | 7.4   | 9.23 | mA                    |  |

www.ti.com

## EARPHONE PATH SPECIFICATION

Over operating free-air temperature range (unless otherwise noted)

### EARPHONE PATH SPECIFICATION

| PARAMETER                                              | TEST CONDITIONS                           | MIN   | TYP   | MAX   | UNIT     |

|--------------------------------------------------------|-------------------------------------------|-------|-------|-------|----------|

| Speaker load resistance (RL)                           |                                           | 16    | 32    | 100   | Ω        |

| Output differential swing 0 dBFs (THD > 40 dB)         | R <sub>L</sub> = Typ                      | 2     |       |       | Vrms     |

| at 6-dB analog gain                                    | R <sub>L</sub> = Min                      | 1.42  |       |       | Vrms     |

| Programmable gain range                                |                                           | -24   |       | 6     | dB       |

| Programmable gain step size                            |                                           |       | 2     |       | dB       |

| Absolute gain accuracy                                 | Gain = Max                                | -0.5  |       | 0.5   | dB       |

| Relative gain accuracy                                 |                                           | -0.5  |       | 0.5   | dB       |

| Gain step size accuracy                                |                                           | -0.25 |       | 0.25  | dB       |

| Gain variation with frequency                          | f = 20 Hz to 20 kHz, relative to 1<br>kHz | -0.8  | -0.55 | 0.3   | dB       |

| Idle channel noise                                     | f = 20 Hz to 20 kHz                       |       | 32    | 45    | µVrms(A) |

| Dynamic range, –60-dBFs output with –24-dB analog gain |                                           | 87    | 97    |       | dB(A)    |

| SNR, 0-dBFs output                                     | f = 20 Hz to 20 kHz                       | 87    | 97    |       | dB(A)    |

| Total harmonic distortion                              | 0 dBFs                                    |       | -60   | -40   |          |

| (sine wave @1 kHz, gain = Max)                         | –10 dBFs                                  |       | -70   | -60   |          |

|                                                        | –20 dBFs                                  |       | -70   | -60   | dB(A)    |

|                                                        | –40 dBFs                                  |       | -50   | -40   |          |

|                                                        | –60 dBFs                                  |       | -30   | -20   |          |

| THD+N                                                  | $R_L = TYP$ , 0 dBFS output               |       | 0.02  | 0.1   | %        |

| THD+N                                                  | $R_L = TYP$ , -6 dBFS output              |       | 0.015 | 0.1   | 70       |

| Differential offset                                    |                                           | -25   |       | 25    | mV       |

| Power supply rejection from VBAT                       | Gain = Max                                | 80    | 100   |       | dB(A)    |

| Croup dolou                                            | SINC filter                               |       |       | 4.125 | μs       |

| Group delay                                            | FIR filter                                |       |       | 1     | μs       |

| Average current from VBAT                              |                                           |       | 3.7   | 4.8   | mA       |

## **AUX-OUTPUT PATH SPECIFICATION**

Over operating free-air temperature range (unless otherwise noted)

| AUX-OUTPUT PATH SPECIFICATION                          |                                           |       |      |      |          |

|--------------------------------------------------------|-------------------------------------------|-------|------|------|----------|

| PARAMETER                                              | TEST CONDITIONS                           | MIN   | TYP  | MAX  | UNITS    |

| Load resistance (R <sub>L</sub> )                      |                                           | 10    | 150  |      | kΩ       |

| Output differential swing 0 dBFs (THD > 40 dB)         | R <sub>L</sub> = Typ                      | 1.7   |      |      | Vrms     |

| Programmable gain range                                |                                           |       | 58   |      | dB       |

| Programmable gain step size                            |                                           |       | 2    |      | dB       |

| Absolute gain accuracy                                 | Gain = 0 dB                               | -1.0  |      | 1.0  | dB       |

| Gain step size accuracy                                | Gain = 6 to -40 dB                        | -0.25 |      | 0.25 | dB       |

|                                                        | Gain = -40 to -50 dB                      | -0.5  |      | 0.5  | dB       |

| Relative gain accuracy                                 | Gain = 6 to -40 dB                        | -0.5  |      | 0.5  | dB       |

|                                                        | Gain = -40 to -50 dB                      | -1.0  |      | 1.0  | dB       |

| Gain variation with frequency                          | f= 20 Hz to 20 kHz relative to 1 kHz      | -0.5  |      | 0.5  | dB       |

|                                                        | Gain = 0 dB                               |       |      |      |          |

| Dynamic range, –60-dBFs output with –24-dB analog gain |                                           | 87    | 90   |      | dB(A)    |

| SNR, 0-dBFs output                                     |                                           | 80    | 90   |      | dB(A)    |

|                                                        | 10-kΩ load, HFPGA = 0 dB, 1-kHz<br>signal |       |      |      |          |

|                                                        | 1-Vpp single-ended output                 |       | 0.07 |      |          |

| THD+N                                                  | 2-Vpp single-ended output                 |       | 0.4  |      | %        |

|                                                        | 1-Vpp differential output                 |       | 0.07 |      |          |

|                                                        | 2-Vpp differential output                 |       | 0.4  |      |          |

| Idle channel noise                                     |                                           |       | 40   | 50   | µVrms(A) |

STRUMENTS

**FEXAS**

## HANDS-FREE PATH SPECIFICATION

Over operating free-air temperature range (unless otherwise noted)

### HANDS-FREE PATH SPECIFICATION

| PARAMETER                                                | TEST CONDITIONS                     | MIN   | TYP  | MAX   | UNIT     |

|----------------------------------------------------------|-------------------------------------|-------|------|-------|----------|

| Input supply                                             | Battery                             | 2.3   |      | 5     | V        |

|                                                          | SMPS boost                          |       |      | 5.5   | v        |

| Maximum output power (PGA = 0 dB)                        | R <sub>L</sub> = 8 Ω                |       |      |       |          |

|                                                          | VDDHF = 5.5 V (THD > 40 dB)         | 1.3   | 1.5  |       |          |

|                                                          | VDDHF = 4.5 V (THD > 40 dB)         | 0.9   | 1    |       | W        |

|                                                          | VDDHF = 3.6 V (THD > 40 dB)         | 0.55  | 0.6  |       | vv       |

|                                                          | VDDHF = 2.8 V (THD > 40 dB)         | 0.24  | 0.28 |       |          |

|                                                          | VDDHF = 2.3 V (THD > 30 dB)         | 0.15  | 0.2  |       |          |

| Programmable gain range (PGA)                            |                                     | -52   |      | 6     | dB       |

| Programmable gain step size (PGA)                        |                                     |       | 2    |       | dB       |

| Absolute gain accuracy                                   | Gain = 0 dB                         | -1    |      | 1     | dB       |

| Relative gain accuracy                                   | Gain = 6 to -40 dB                  | -0.5  |      | 0.5   |          |

|                                                          | Gain = -40 to -50 dB                | -1    |      | 1     | dB       |

| Gain step size accuracy                                  | Gain = 6 to -40 dB                  | -0.25 |      | 0.25  | dB       |

|                                                          | Gain = -40 to -50 dB                | -0.5  |      | 0.5   | aв       |

| Gain variation with frequency                            | f = 20 kHz relative to 1 kHz        | -1.25 | -1   | -0.75 | dB       |

| Dynamic range, –60-dBFs output with –24-dB<br>HFPGA gain |                                     | 85    | 93   |       | dB(A)    |

| Idle channel noise                                       | Gain = –24 dB                       |       | 65   | 170   | µVrms(A) |

| Total harmonic distortion in $f = 20$ Hz to 20 kHz       | R <sub>L</sub> = 8 Ω, VDDHF > 3.6 V |       |      |       |          |

| (sine wave @ 1 kHz, 0-dB PGA gain setting)               | 25 mW < P <sub>OUT</sub> < 0.5 W    |       | -55  | -50   | dB(A)    |

|                                                          | 1 mW < P <sub>OUT</sub> < 25 mW     |       | -45  | -40   |          |

| Power supply rejection from VBAT                         | Gain = 0 dB                         |       |      |       |          |

|                                                          | Idle channel                        | 55    | 65   |       | dB(A)    |

|                                                          | Intermodulation                     | 70    | 80   |       | dBc      |

| Corrier frequences                                       | 19.6 MHz PDM clock                  |       | 384  |       | kHz      |

| Carrier frequencey                                       | 17.64 MHz PDM clock                 |       | 353  |       | kHz      |

| Average quiescent current from VBAT                      | Mono                                |       | 2    | 3     | mA       |

www.ti.com

## **VIBRA DRIVER PATHS**

Over operating free-air temperature range (unless otherwise noted)

|       | _      |       |

|-------|--------|-------|

| VIBRA | DRIVER | PATHS |

| PARAMETER                                         | TEST CONDITIONS                                  | MIN  | TYP | MAX  | UNIT  |

|---------------------------------------------------|--------------------------------------------------|------|-----|------|-------|

| Input supply VDD                                  | Battery or SMPS boost                            | 2.3  |     | 5.5  | V     |

| DC output voltage                                 | Left channel, $R_L = 16 \Omega$                  |      |     |      |       |

|                                                   | VDDVIB = 4.8 V                                   | 3.3  | 3.6 |      | N     |

|                                                   | VDDVIB = 3.8 V                                   | 2.6  | 2.9 |      | V     |

|                                                   | VDDVIB = 2.5 V                                   | 1.6  | 1.7 |      |       |

|                                                   | Right channel, $R_L = 8 \Omega$                  |      |     |      |       |

|                                                   | VDDVIB = 4.8 V                                   | 3.6  | 3.9 |      | V     |

|                                                   | VDDVIB = 3.8 V                                   | 2.7  | 3   |      | V     |

|                                                   | VDDVIB = 2.3 V                                   | 1.6  | 1.8 |      |       |

| Absolute gain accuracy                            |                                                  | -0.5 |     | 0.5  | dB    |

| Voltage step                                      |                                                  |      | 50  |      | mV    |

| Gain variation with frequency                     | f = 250 Hz to 8 kHz relative to 1 kHz            | -0.5 | 0   | 0.5  | dB    |

| Total harmonic distortion in $f = 20 Hz$ to 8 kHz | $R_{L} = 8 \Omega, V_{DD} > 3.6 V, -1 dBV_{rms}$ |      | -35 | -30  | dB(A) |

| Latency                                           | PDM input                                        |      |     | 20.8 |       |

|                                                   | PCM input                                        |      |     | 10.4 | μs    |

| Load resistance R <sub>L</sub>                    |                                                  | 8    | 16  |      | Ω     |

| Average quiescent current from VBAT               | Mono                                             |      | 1   | 1.5  | mA    |

## INPUT CLOCK PARAMETERS

Over operating free-air temperature range (unless otherwise noted)

| SYSTEM CLOCK                    |                                           |      |     |      |        |

|---------------------------------|-------------------------------------------|------|-----|------|--------|

| PARAMETER                       | TEST CONDITIONS                           | MIN  | TYP | MAX  | UNIT   |

| Input frequency accuracy        |                                           | -100 |     | 100  | ppm    |

| Input swing                     | Square wave                               | 1.65 |     | 1.89 | V      |

|                                 | Sine wave, input common mode 0.5 to 0.7 V | 0.4  |     | 1    | Vpp    |

|                                 | 12 MHz                                    |      | -89 | -86  |        |

| lanut CCD share sains @ 4 kl la | 19.2 MHz                                  |      | -86 | -83  |        |

| Input SSB phase noise @ 1 kHz   | 26 MHz                                    |      | -83 | -80  | dBc/Hz |

|                                 | 38.4 MHz                                  |      | -80 | -77  | 1      |

## SLEEP CLOCK

Over operating free-air temperature range (unless otherwise noted)

| SLEEP CLOCK              |                      |       |        |      |        |

|--------------------------|----------------------|-------|--------|------|--------|

| PARAMETER                | TEST CONDITIONS      | MIN   | TYP    | MAX  | UNIT   |

| Input frequency          |                      |       | 32,768 |      | Hz     |

| Input frequency accuracy |                      | -1000 |        | 1000 | ppm    |

| Input duty cycle         |                      | 40    |        | 60   | %      |

| Input CCD phase poins    | @ 100Hz              |       | –108   | -105 | dBc/Hz |

| Input SSB phase noise    | @ 1 kHz              |       | –128   | -125 |        |

| Input integrated jitter  | 20 Hz to 20 kHz flat |       | 0.61   | 0.86 |        |

|                          | 80 Hz to 20 kHz flat |       | 0.31   | 0.43 | nsrms  |

## **APPLICATION INFORMATION**

### **UPLINK PATH DESCRIPTION**

The voice uplink path includes two low-noise input amplifier stages (MicAmpL and MicAmpR) and two ADCs dedicated to the three microphone inputs and stereo auxiliary/FM inputs. Two low-power input amplifiers (LineInAmpL and LineInAmpR) enable stereo analog loops (LB0, LB1) to the downlink section, independent and concurrent with stereo microphone uplink to OMAP4. The auxiliary/FM radio left and right channels can be connected to the microphone preamplifiers for recording, or to a line-in amplifier for direct analog loop to downlink drivers, or simultaneously to both.

Analog microphone bias outputs, MBIAS and HBIAS, have a dedicated supply pin (VDDABIAS), which can be connected to the battery or to an external boost. If full PSR performance is required in a system with minimum battery level below 2.5 V, the latter connection is recommended.

Microphone bias blocks can be set to sleep mode for low quiescent current consumption. In sleep mode, only the output voltage specification is ensured with the specified sleep mode load current.

Mapping of analog inputs to uplink data channels UL0 and UL1 connected to the OMAP4 is indicated in the following table:

|                           | UL0 | UL1 | LB0 | LB1 |

|---------------------------|-----|-----|-----|-----|

| Main microphone, MMIC     | X   |     |     |     |

| SubMicrophone, SMIC       |     | Х   |     |     |

| Headset microphone, HSMIC | Х   | Х   |     |     |

| Left auxiliary/FM radio   | Х   |     | Х   |     |

| Right auxiliary/FM radio  |     | Х   |     | Х   |

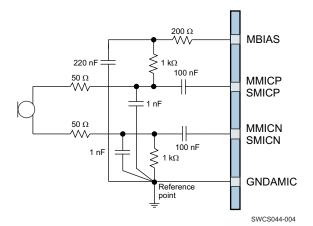

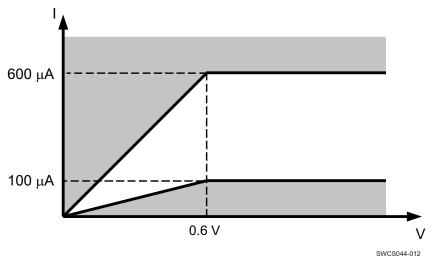

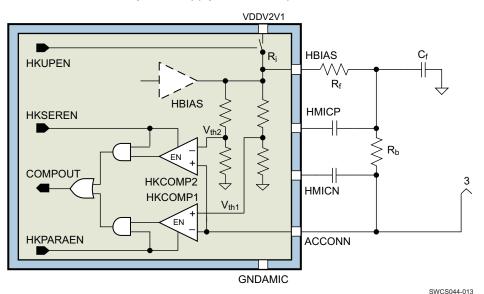

For microphone bias connection, if the negative terminal of the microphone is available, which is usually the case for device internal microphones, the board schematic for a fully differential input shown in Figure 3 is proposed. This approach minimizes differential coupling but provides almost no rejection from bias noise voltage (MBIAS).

Figure 3. Board With Available Negative Terminal

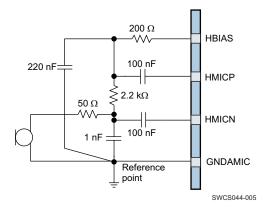

If the negative terminal of the microphone is not available (that is, it is directly connected to ground), which is usually the case for accessory microphones, the board schematic for a pseudodifferential input shown in Figure 4 is suggested. This approach can suffer from differential coupling, but provides good rejection from bias noise voltage (HBIAS).

Figure 4. Board With Unavailable Negative Terminal

In all board layouts, the star connection of all the ground lines to a single via to the ground plane (reference point) is highly recommended to minimize degradation from unequal potential grounds.

The schematics and component values in Figure 3 and Figure 4 are general proposals and may not be the optimal choice for specific user applications.

Two LDOs provide an external voltage of 1.8/1.85 V to bias digital microphones (DBIAS1 and DBIAS2). One bias generator can bias several digital microphones at the same time, with a total maximum output current of 10 mA. Digital microphone inputs and clocks are supported by OMAP.

## **DOWNLINK PATH DESCRIPTION**

Mapping of audio data inputs from the OMAP4 to audio driver outputs is shown in the following table.

|                  | DL0              | DL1 | DL2              | DL3              | DL4 | I <sup>2</sup> C or Frame <sup>(1)</sup> | LB0 | LB1 |

|------------------|------------------|-----|------------------|------------------|-----|------------------------------------------|-----|-----|

| Earphone         | X <sup>(2)</sup> |     |                  |                  |     |                                          |     |     |

| Left headset     | Х                |     |                  |                  |     |                                          | Х   |     |

| Right headset    | Х                | Х   |                  |                  |     |                                          |     | Х   |

| Left hands-free  |                  |     | Х                |                  |     |                                          | Х   |     |

| Right hands-free |                  |     | Х                | Х                |     |                                          |     | Х   |

| Left auxiliary   |                  |     | X <sup>(3)</sup> |                  |     |                                          | Х   |     |

| Right auxiliary  |                  |     | X <sup>(3)</sup> | X <sup>(3)</sup> |     |                                          |     | Х   |

| Right vibrator   |                  |     |                  |                  | Х   | Х                                        |     |     |

| Left vibrator    |                  |     |                  |                  | Х   | Х                                        |     |     |

(1) The frame line can be used for register write (for example, vibrator data registers) in command mode.

(2) This path cannot be concurrent with L/R headset paths.

(3) These paths can be concurrent, but not independent of L/R hands-free paths.

#### **Headphone/Headset Paths**

For music playback, the analog headset path can be configured in two different modes:

- Low-power mode (LP)

- High-performance mode (HP)

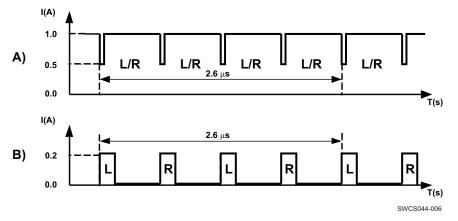

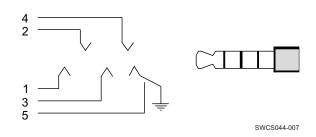

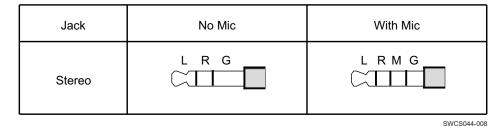

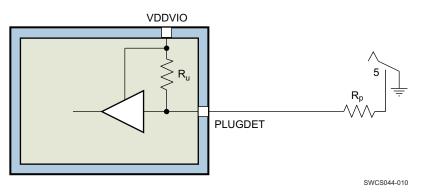

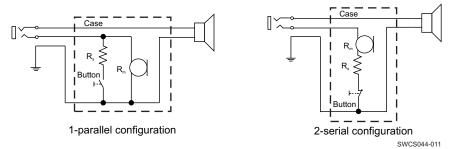

The LP mode system is designed to maximize playback time while maintaining better audio performance than provided by current compression algorithms. The only input clock required in this mode is the RTC at 32,768 Hz.