# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI 8-BIT SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 7470 SERIES

| keep sa | fety first | in vour | circuit | designs! |

|---------|------------|---------|---------|----------|

|         |            |         |         |          |

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

- ◆These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of JAPAN and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

# **Table of contents**

# CHAPTER 1. HARDWARE ■

| 1.1  | Description                                          | 1-2   |

|------|------------------------------------------------------|-------|

| 1.2  | Group expansion                                      | 1-3   |

| 1.3  | Performance overview                                 | 1-6   |

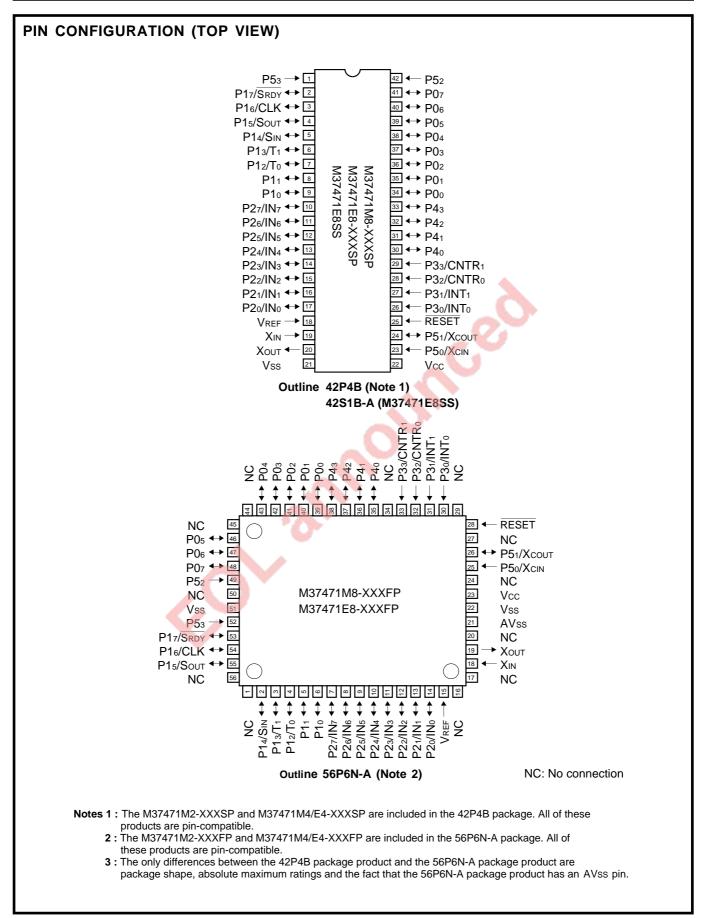

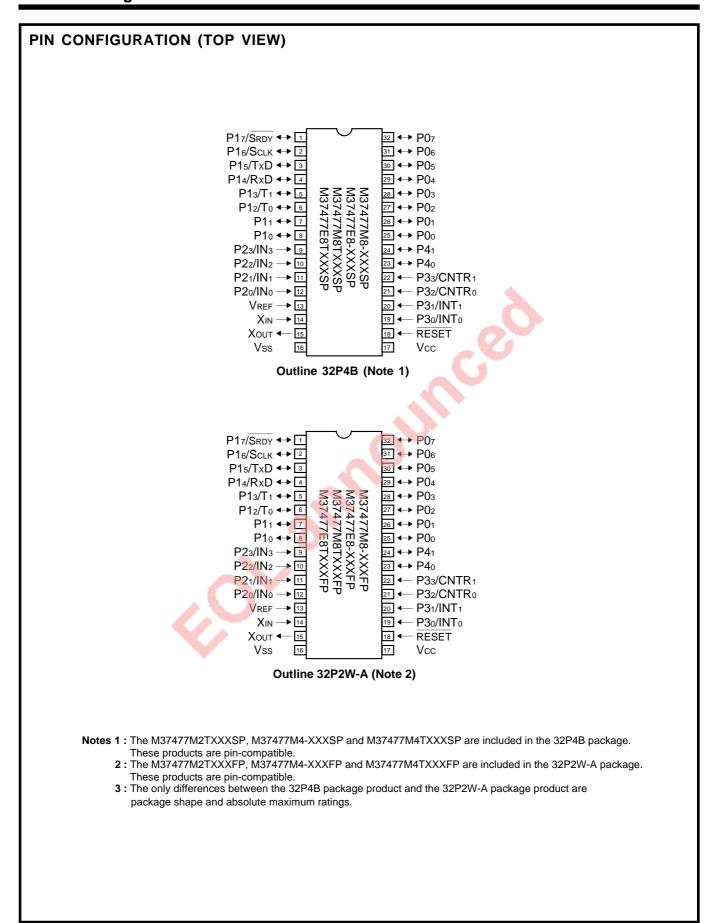

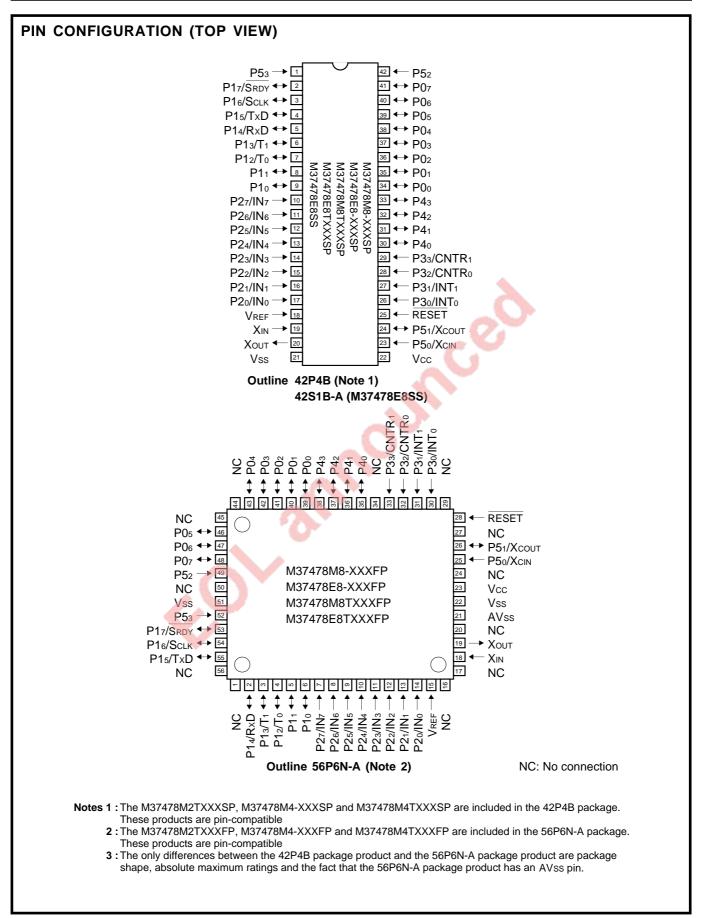

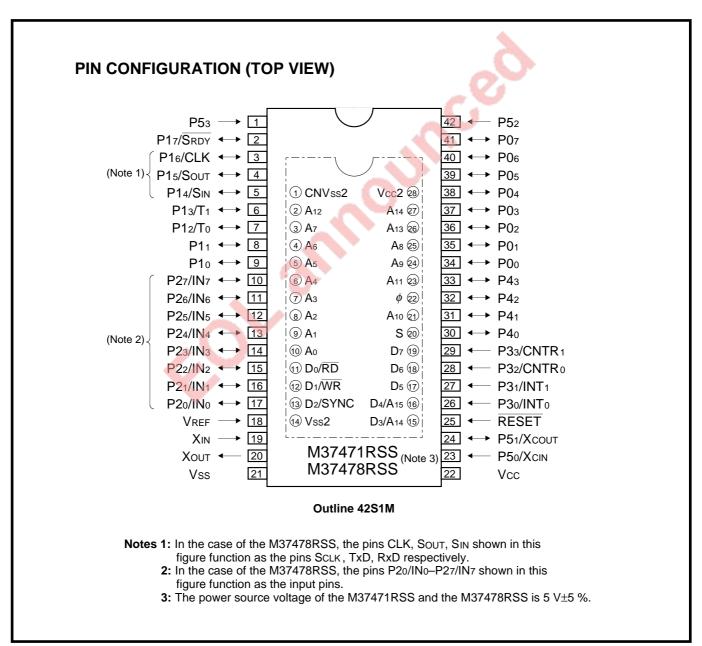

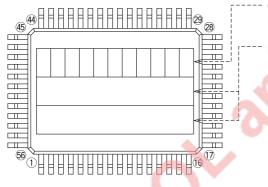

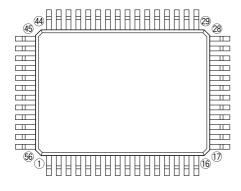

| 1.4  | Pin configuration                                    | 1-10  |

| 1.5  | Pin description                                      | 1-14  |

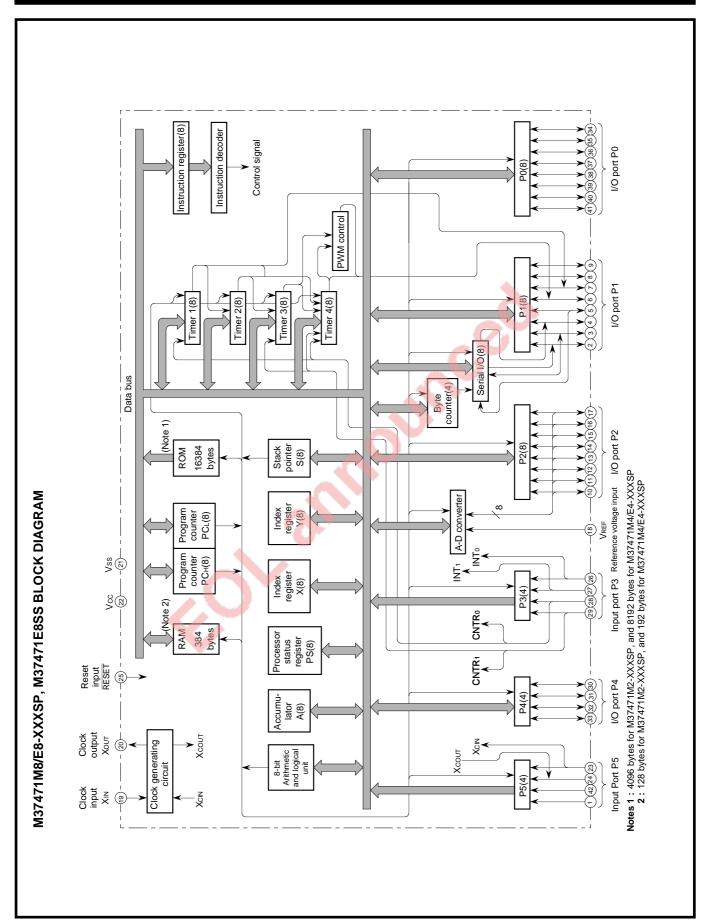

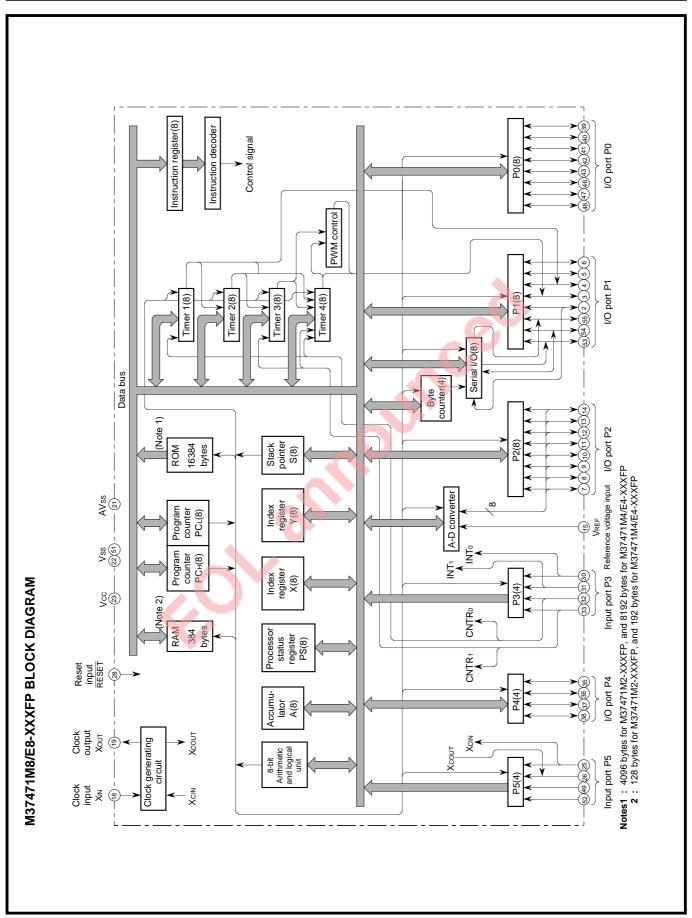

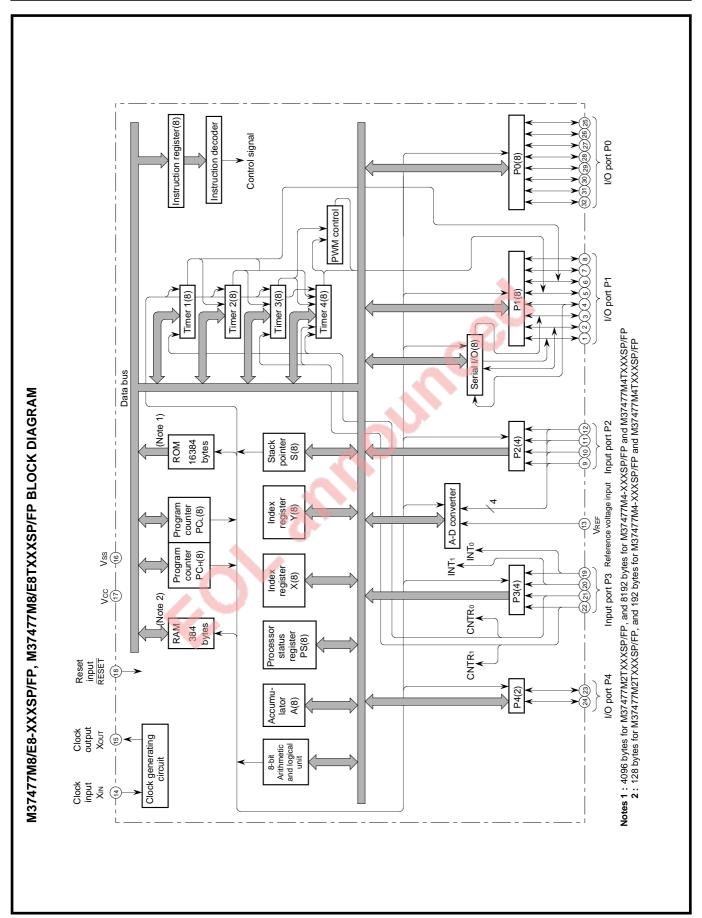

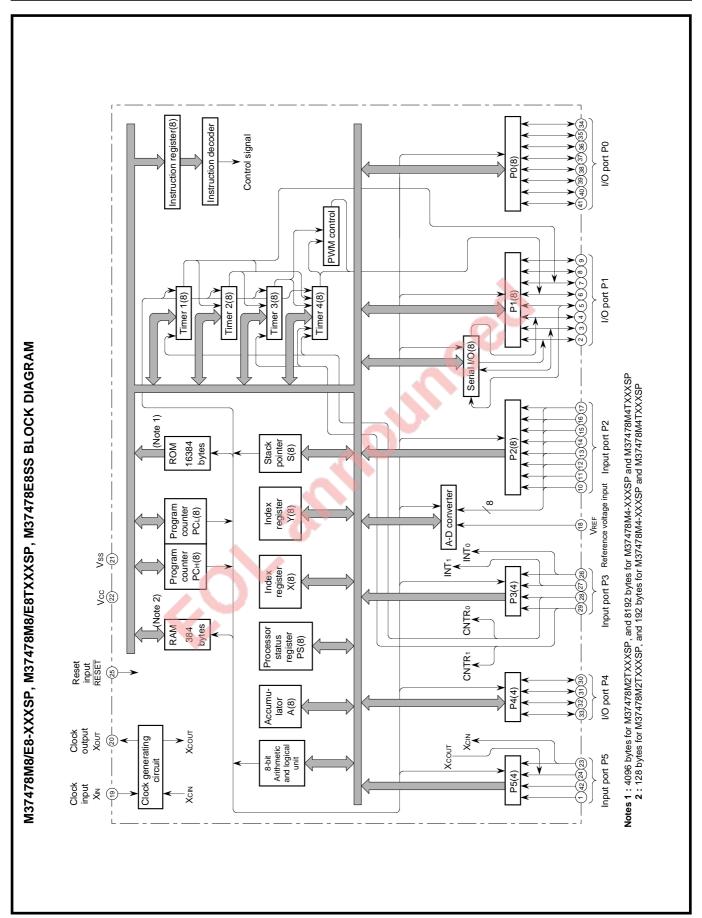

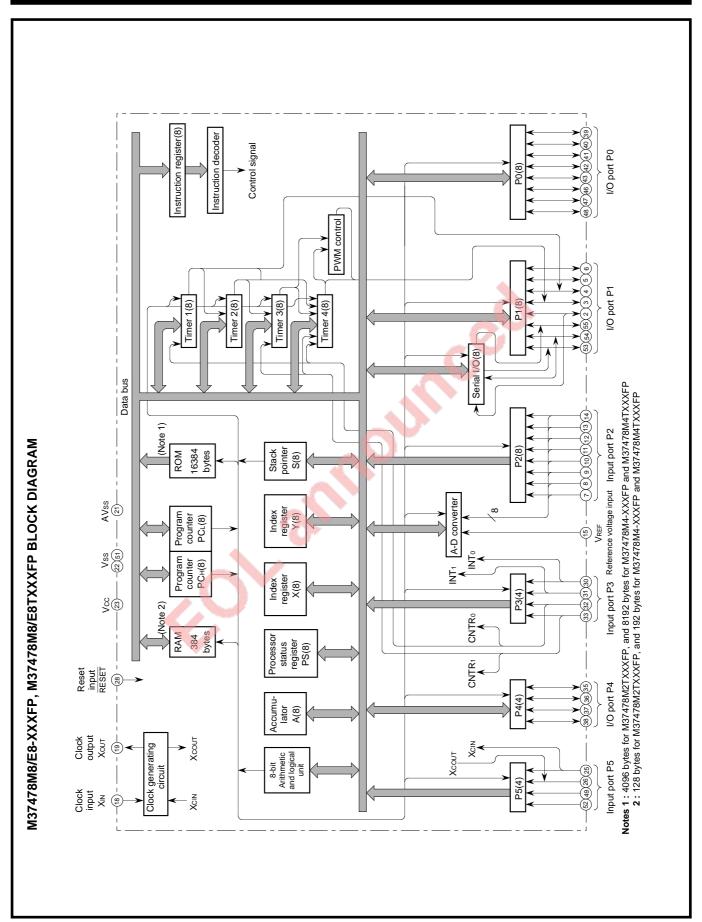

| 1.6  | Functional block diagram                             | 1-17  |

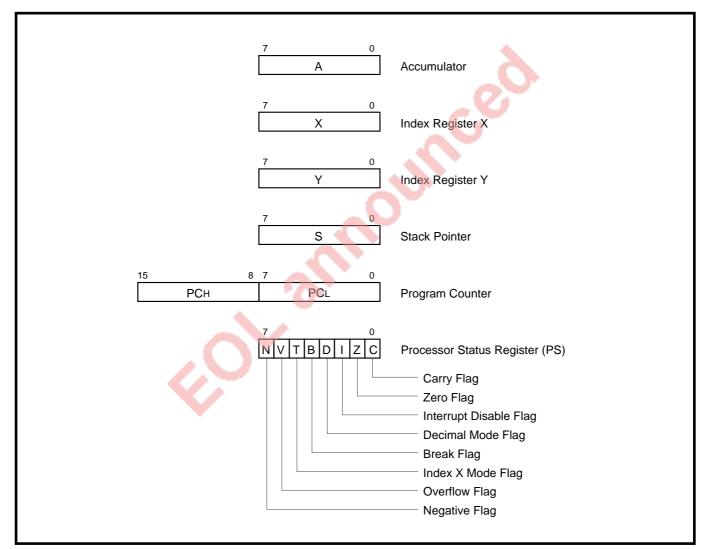

| 1.7  | Central processing unit (CPU)                        | 1-23  |

|      | 1.7.1 Accumulator (A)                                | 1-24  |

|      | 1.7.2 Index register X (X), Index register Y (Y)     | 1-24  |

|      | 1.7.3 Stack pointer (S)                              | 1-24  |

|      | 1.7.4 Program counter (PC)                           |       |

|      | 1.7.5 Processor status register (PS)                 | 1-26  |

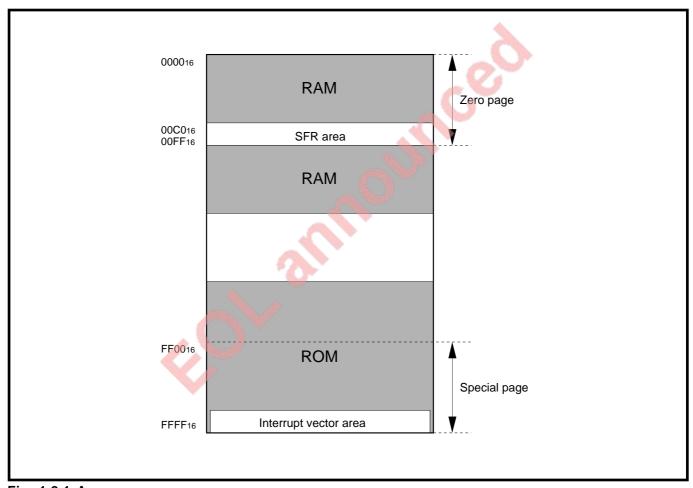

| 1.8  | Access area                                          | 1-28  |

|      | 1.8.1 Zero page (Addresses 000016 to 00FF16)         | 1-29  |

|      | 1.8.2 Special page (Addresses FF0016 to FFFF16)      | 1-29  |

| 1.9  | Memory allocation                                    | 1-30  |

| 1.10 | I/O pins                                             | 1-35  |

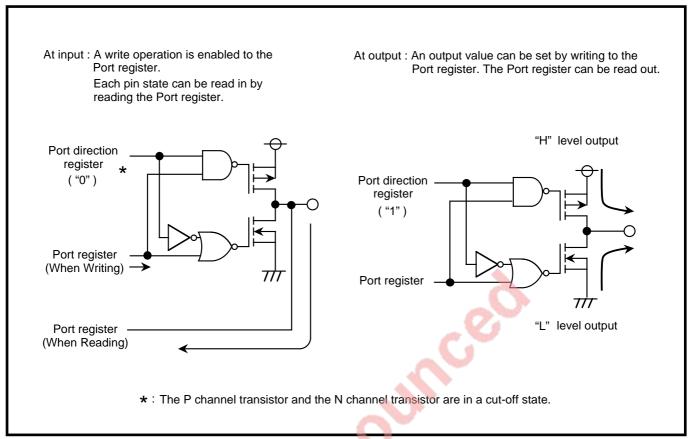

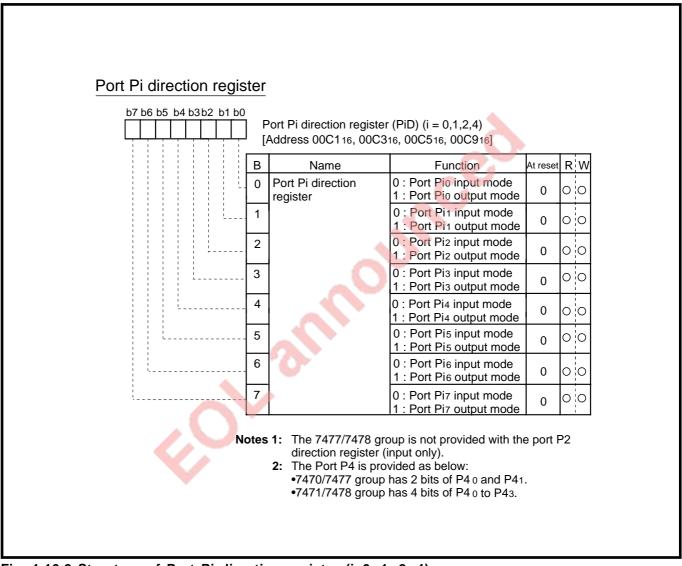

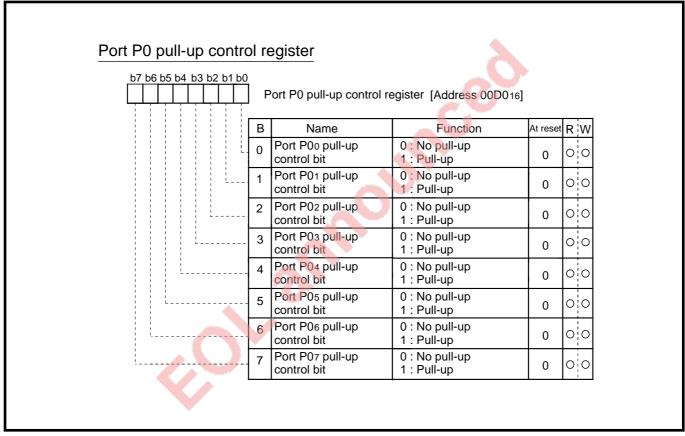

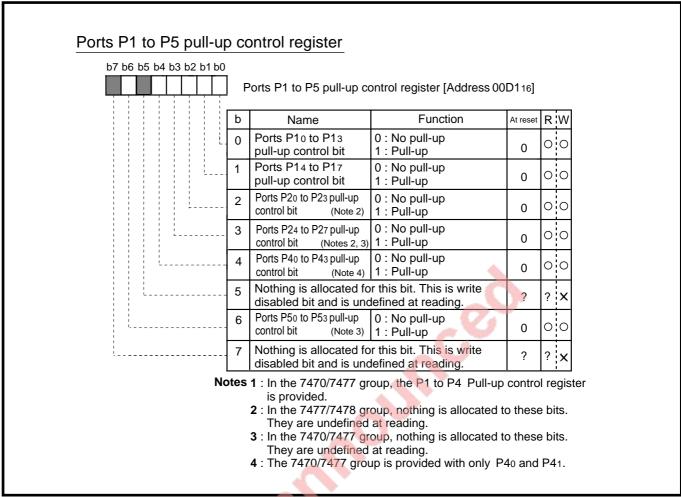

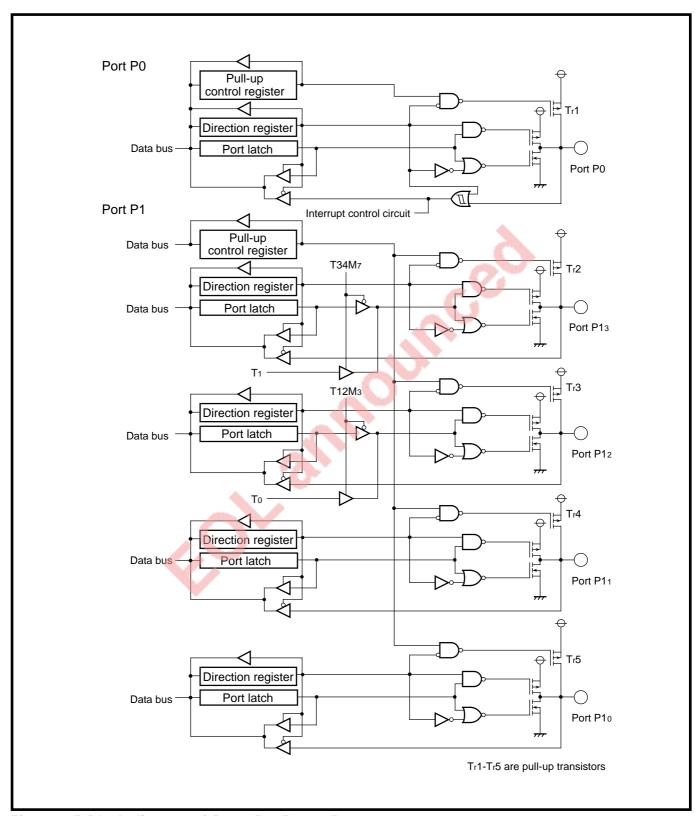

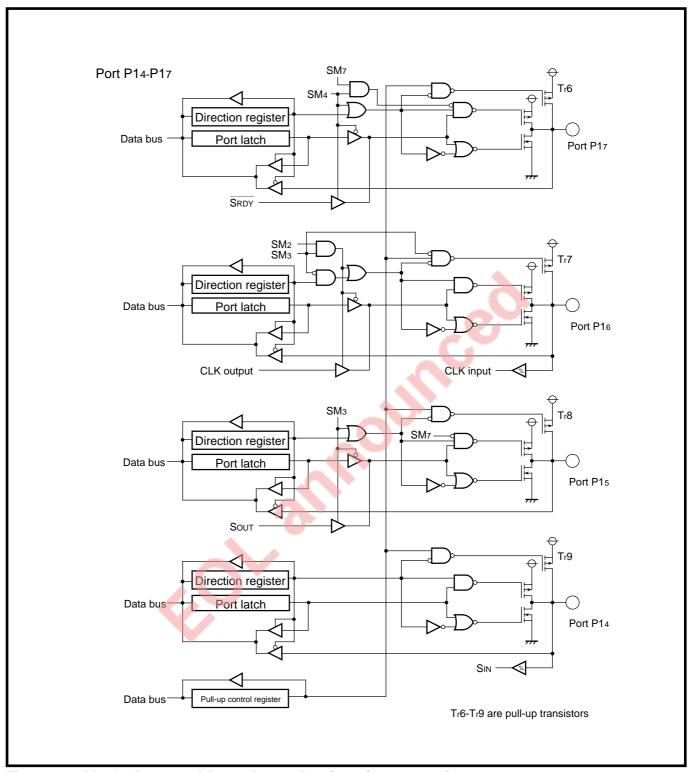

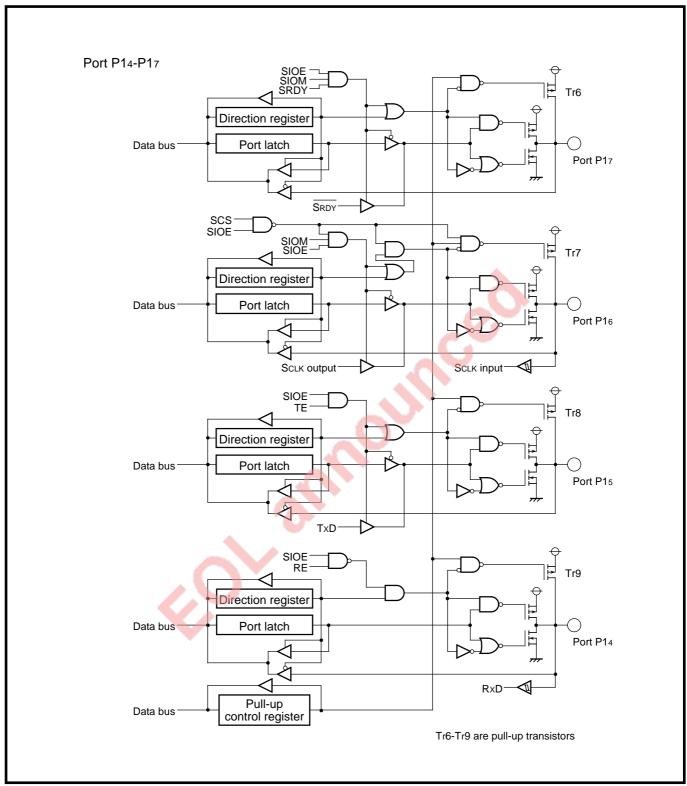

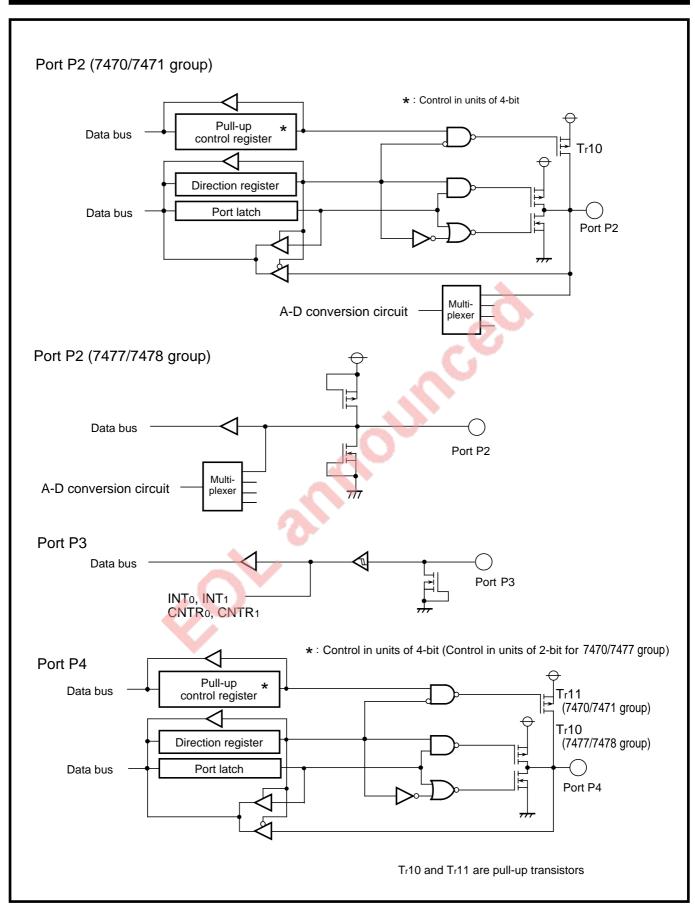

|      | 1.10.1 I/O port                                      | 1-35  |

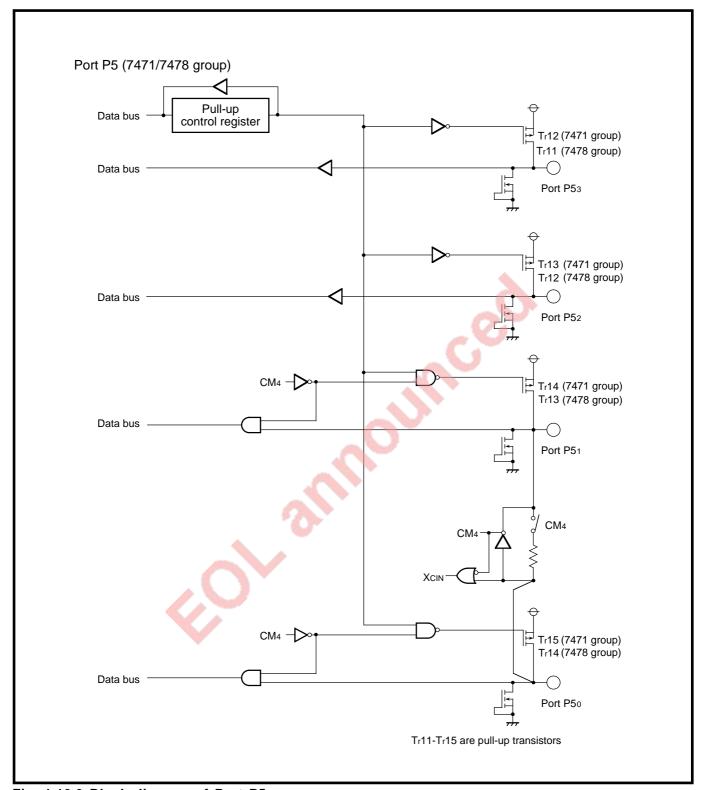

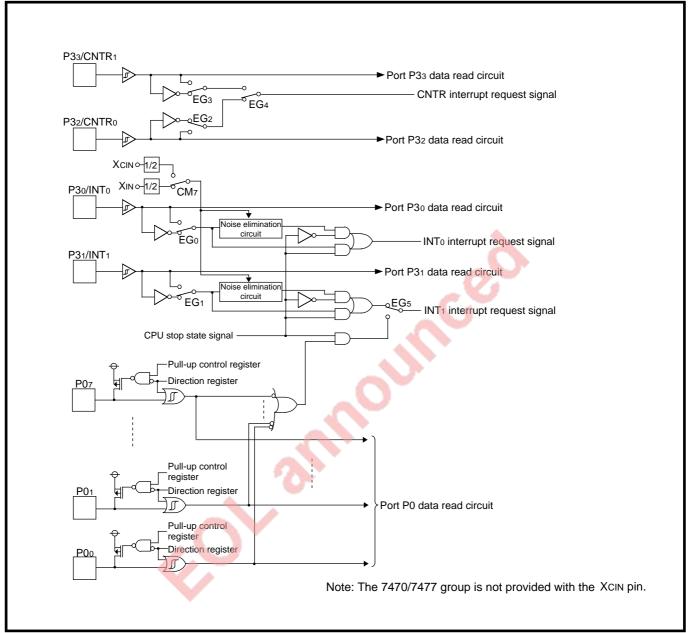

|      | 1.10.2 Port block diagram                            | 1-40  |

|      | 1.10.3 Notes on use                                  | 1-45  |

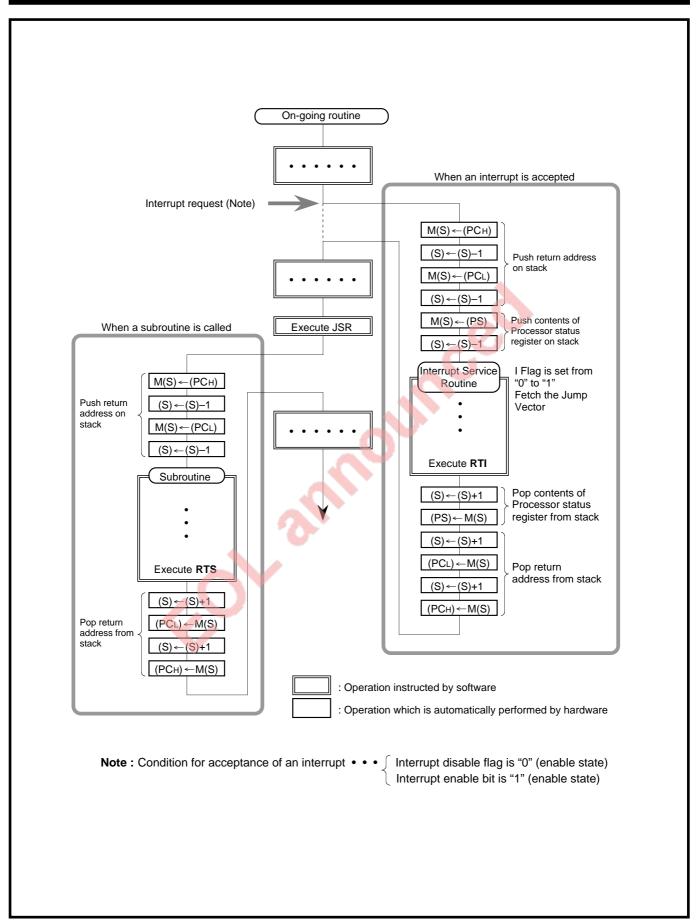

| 1.11 | Interrupts                                           | 1-48  |

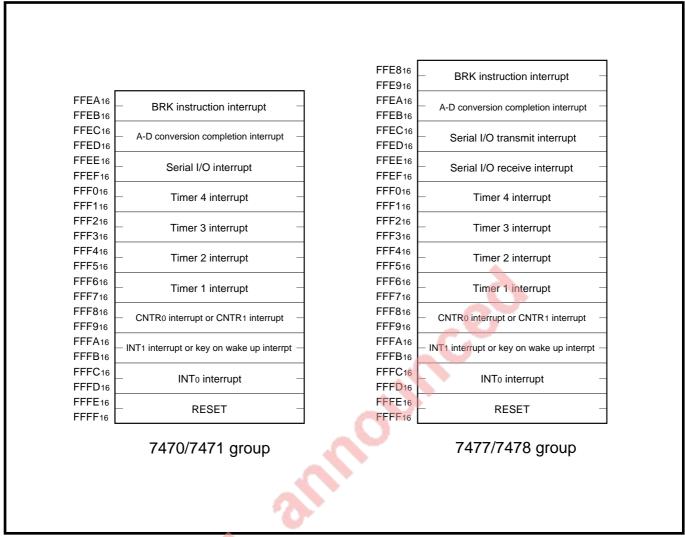

|      | 1.11.1 Description of interrupt source               | 1-48  |

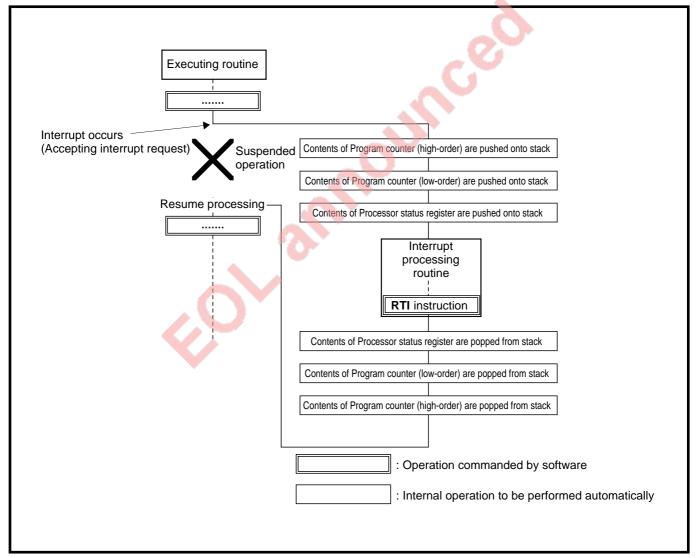

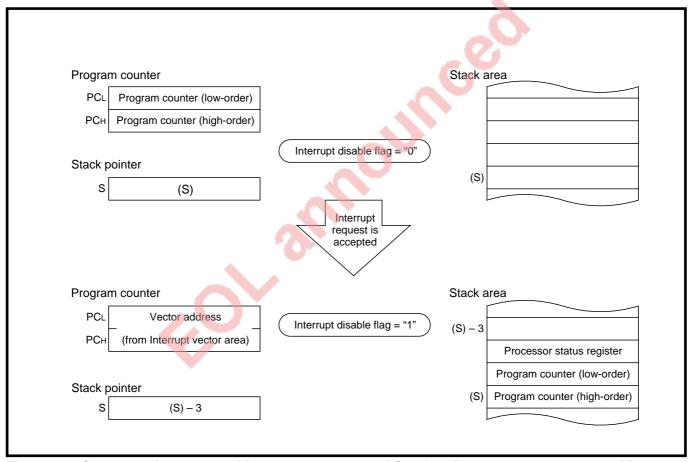

|      | 1.11.2 Operation description                         | 1-52  |

|      | 1.11.3 Interrupt control                             | 1-55  |

|      | 1.11.4 Notes on use                                  | 1-57  |

|      | 1.11.5 Related registers                             | 1-59  |

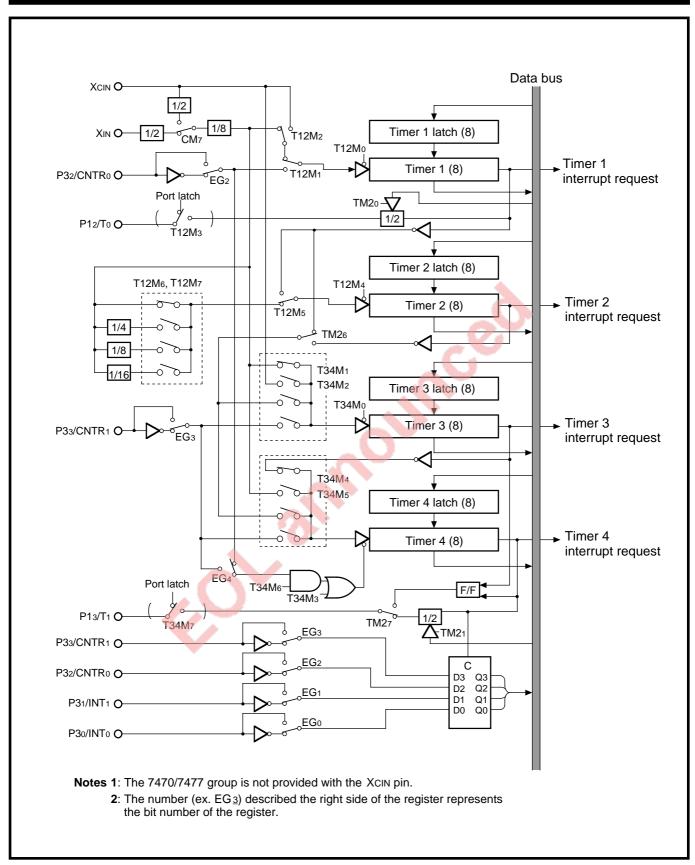

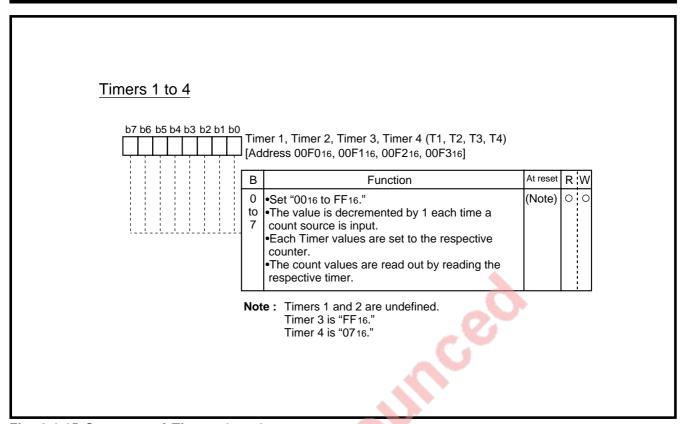

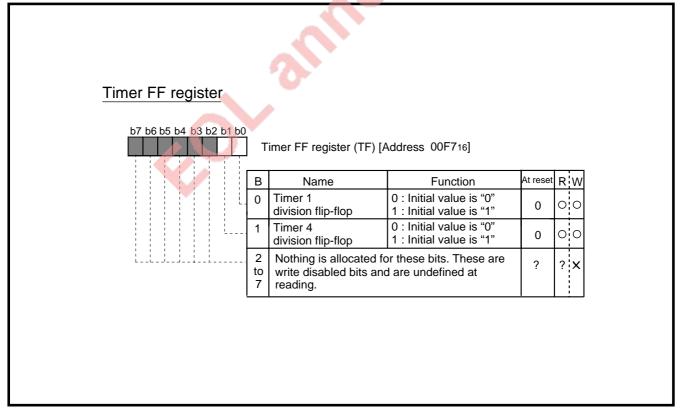

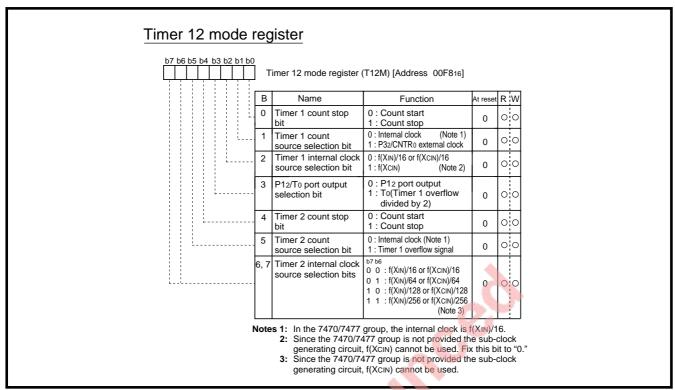

| 1.12 | Timers                                               | 1-62  |

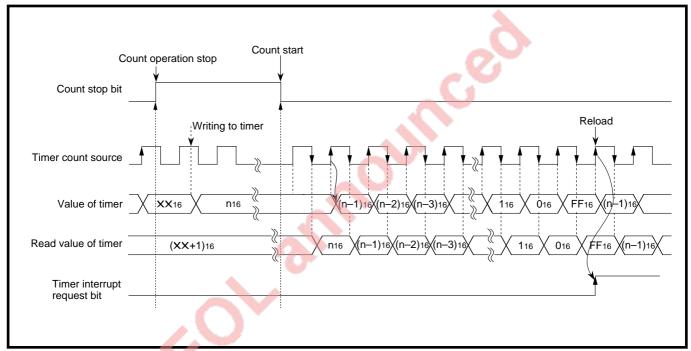

|      | 1.12.1 Operation description                         | 1-64  |

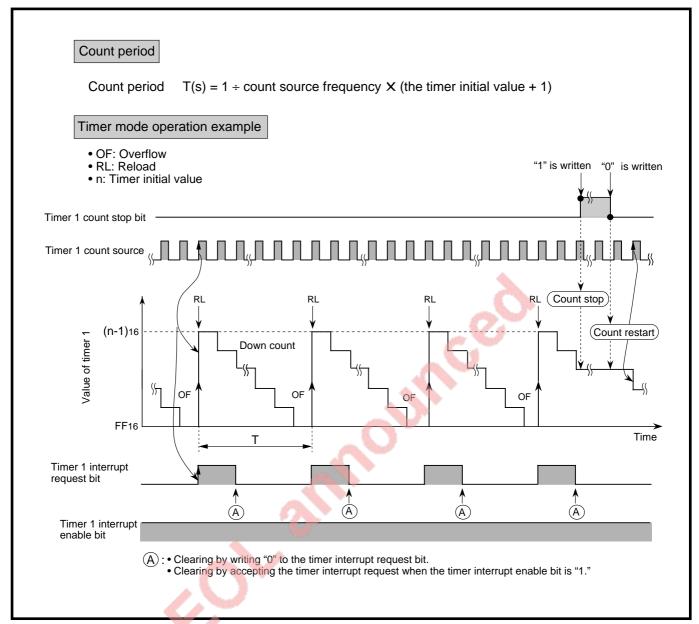

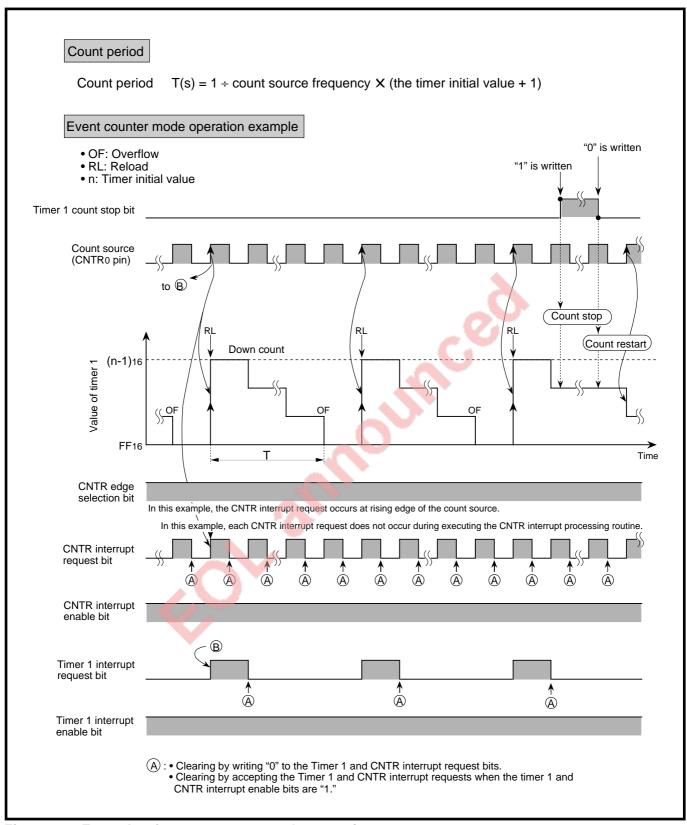

|      | 1.12.2 Description of modes                          | 1-65  |

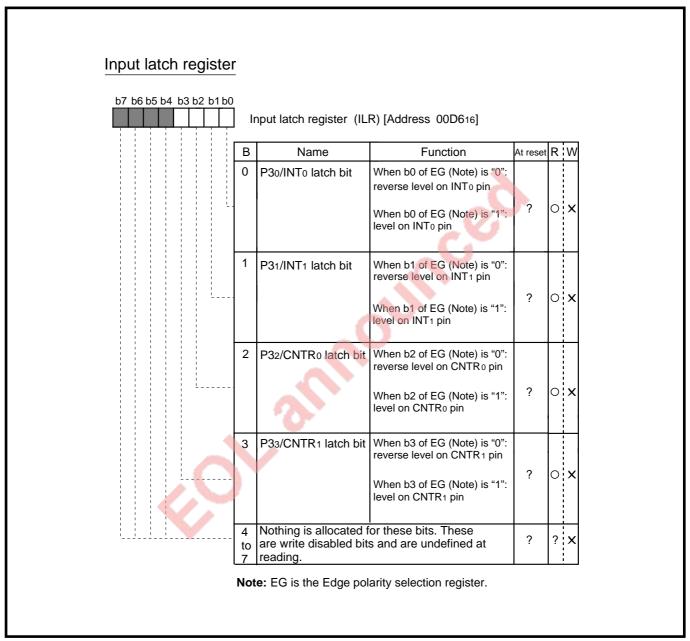

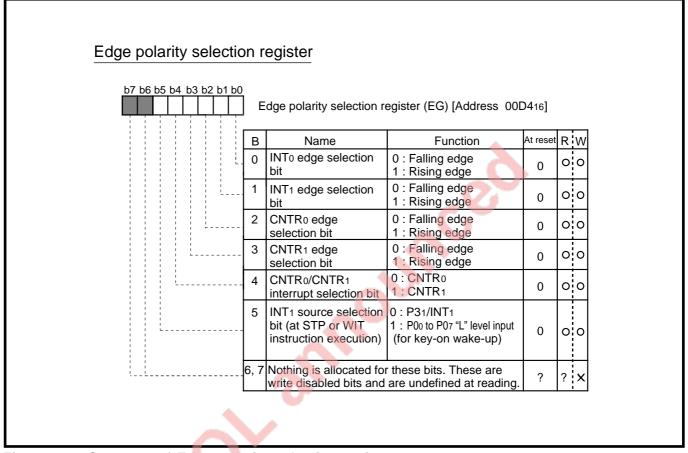

|      | 1.12.3 Input latch function                          | 1-79  |

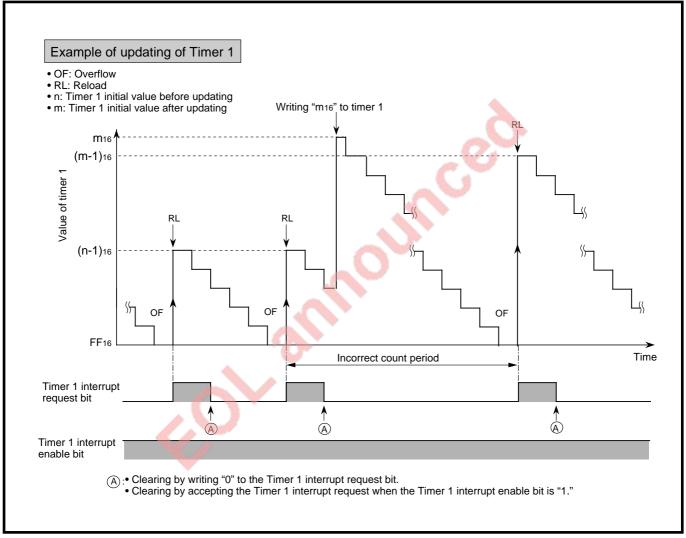

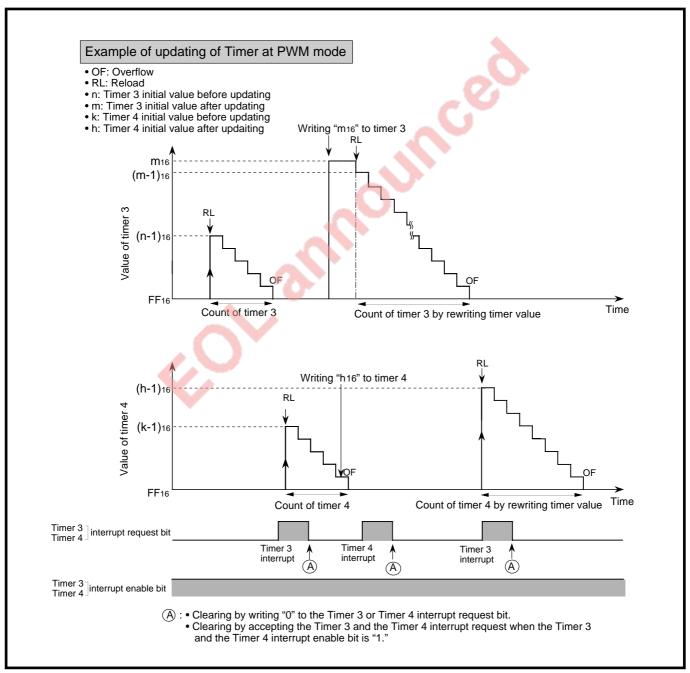

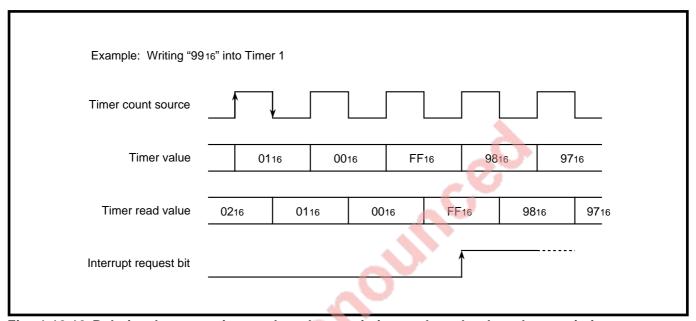

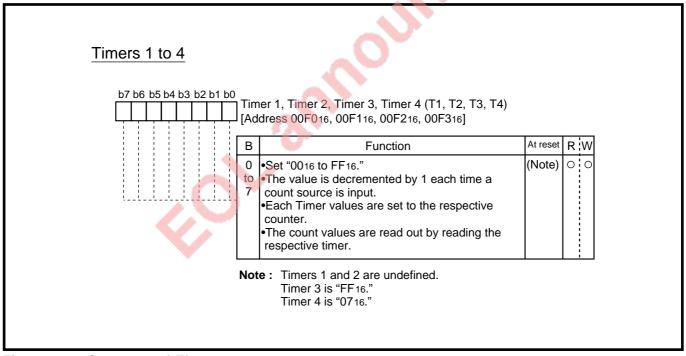

|      | 1.12.4 Updating of contents of Timer and Timer latch | 1-80  |

|      | 1.12.5 Notes on use                                  | 1-82  |

|      | 1.12.6 Related registers                             | 1-83  |

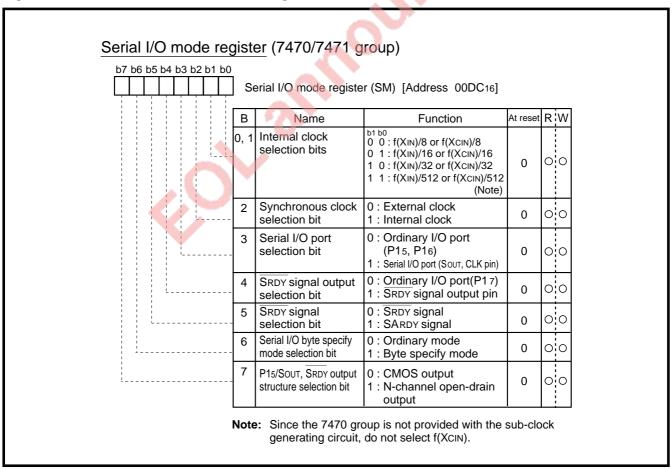

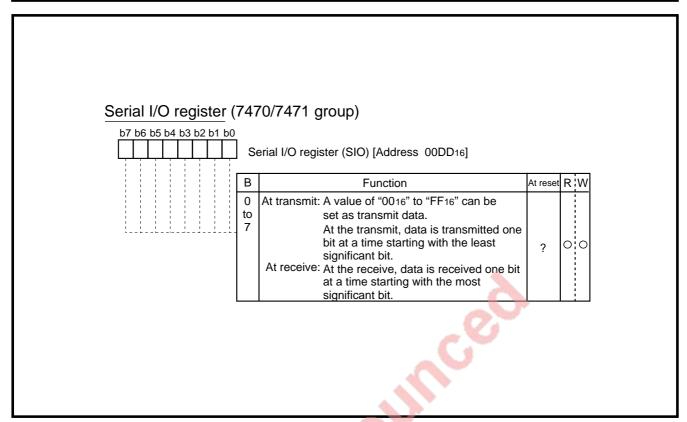

| 1.13 | Serial I/O                                           | 1-89  |

|      | 1.13A 7470/7471 group part                           | 1-90  |

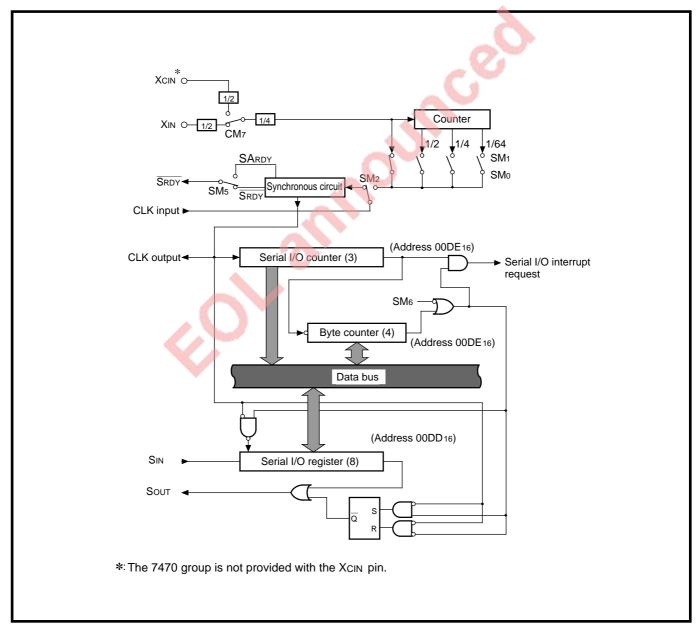

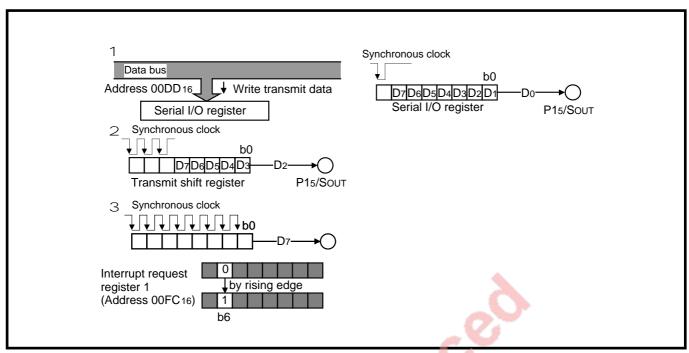

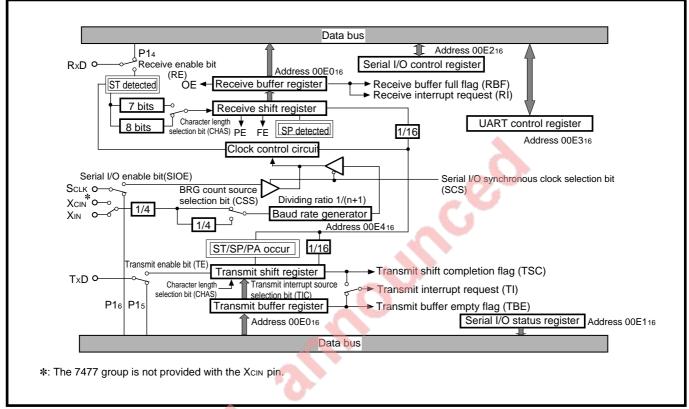

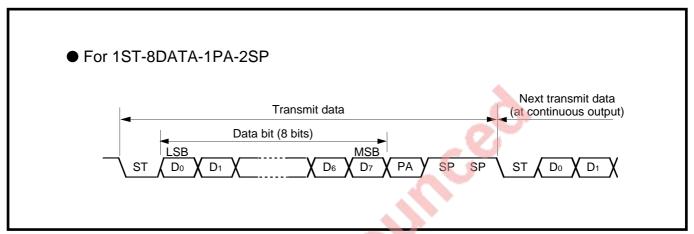

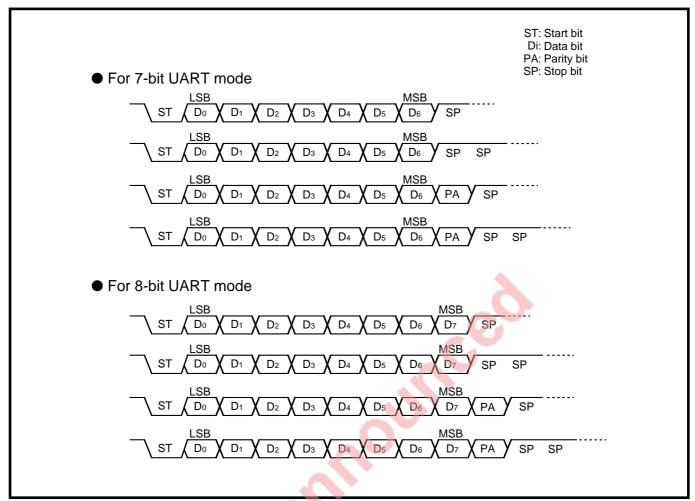

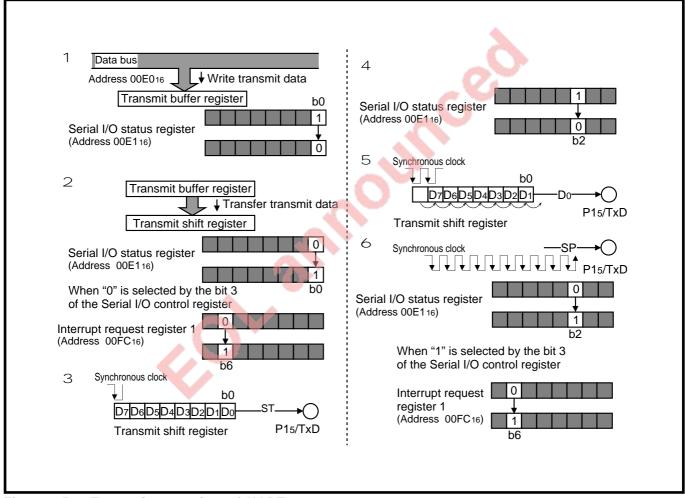

|      | 1.13A.1 Operation description                        | 1-90  |

|      | 1.13A.2 Byte specification mode                      | 1-98  |

|      | 1.13A.3 Pins                                         | 1-101 |

# Table of contents

|      | 1.13A.4 Notes on use                                   | 1-101 |

|------|--------------------------------------------------------|-------|

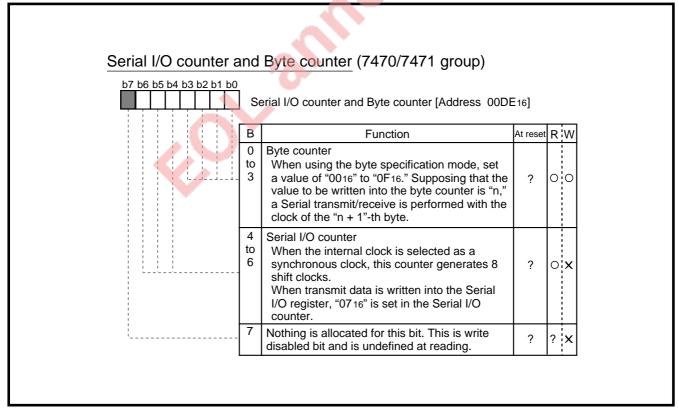

|      | 1.13A.5 Related registers                              | 1-102 |

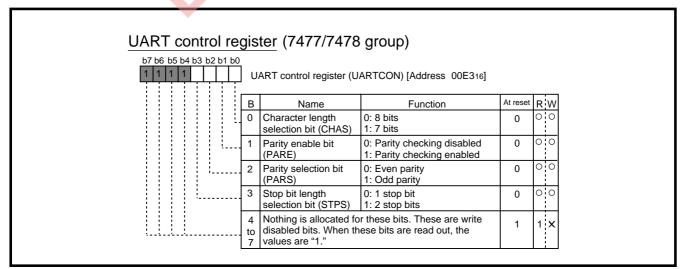

|      | 1.13B 7477/7478 group part                             | 1-105 |

|      | 1.13B.1 Operation description                          | 1-105 |

|      | 1.13B.2 Pins                                           | 1-127 |

|      | 1.13B.3 Notes on use                                   | 1-128 |

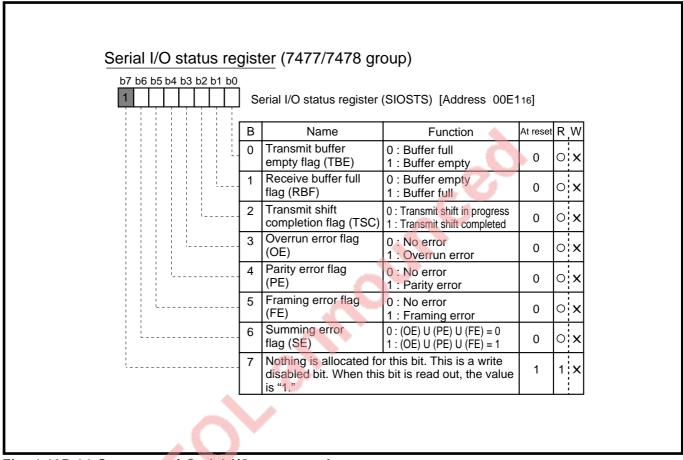

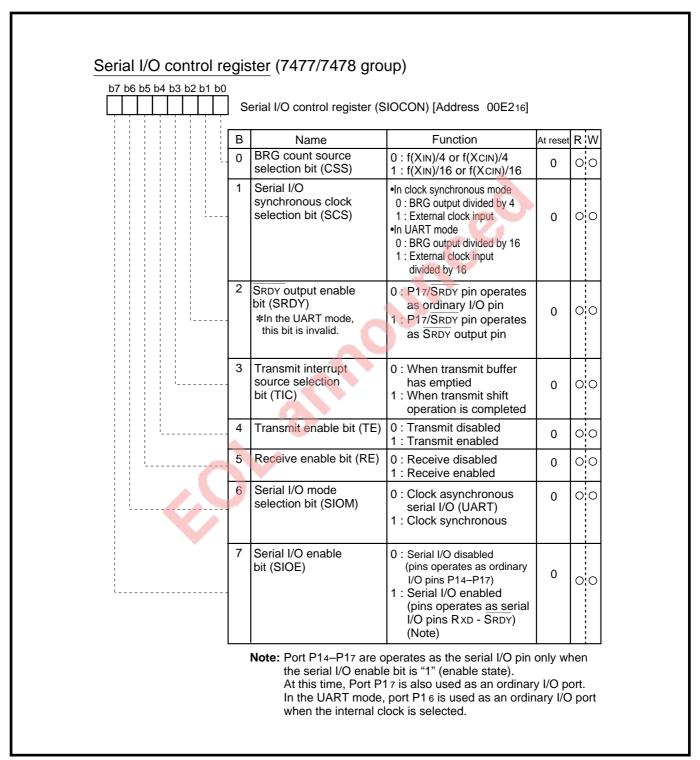

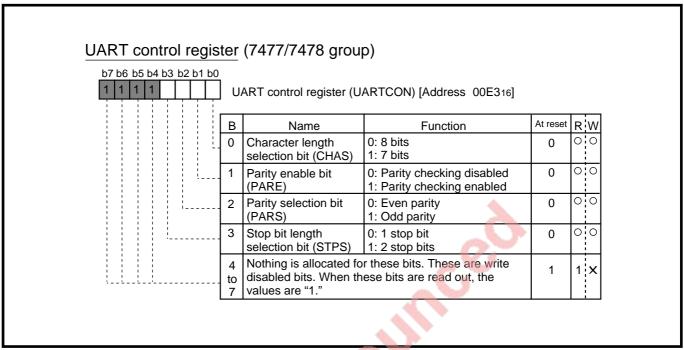

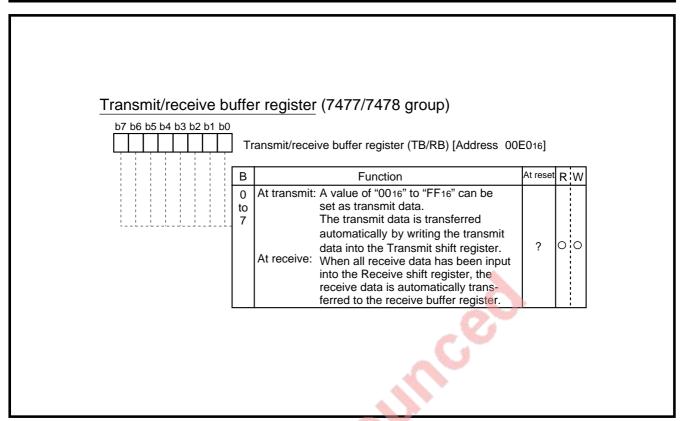

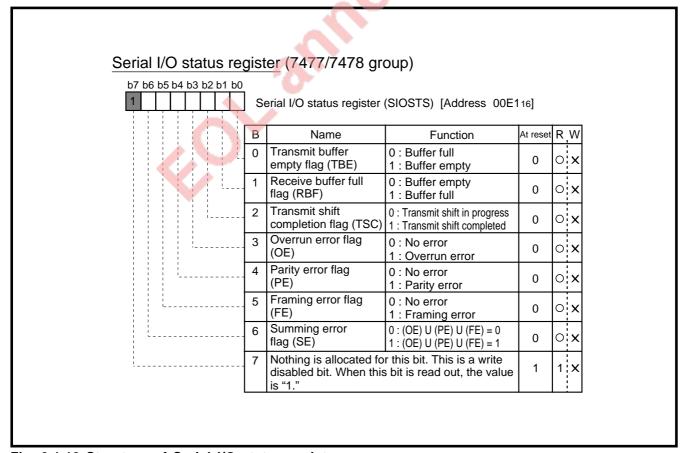

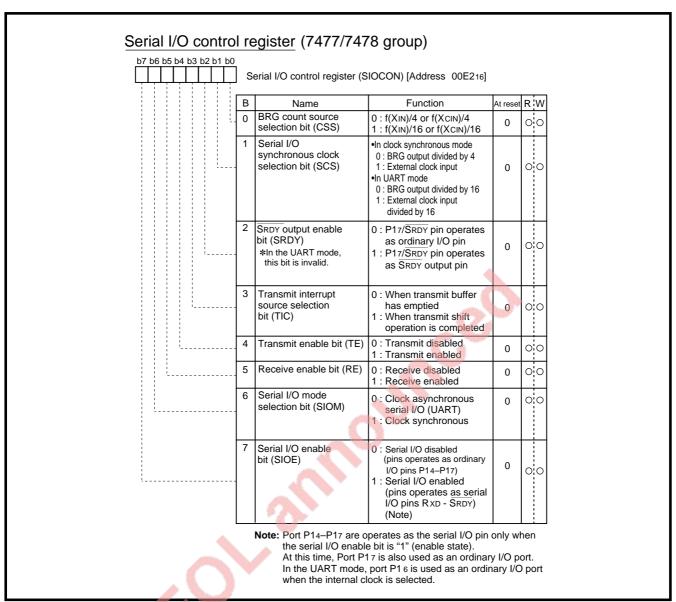

|      | 1.13B.4 Related registers                              | 1-131 |

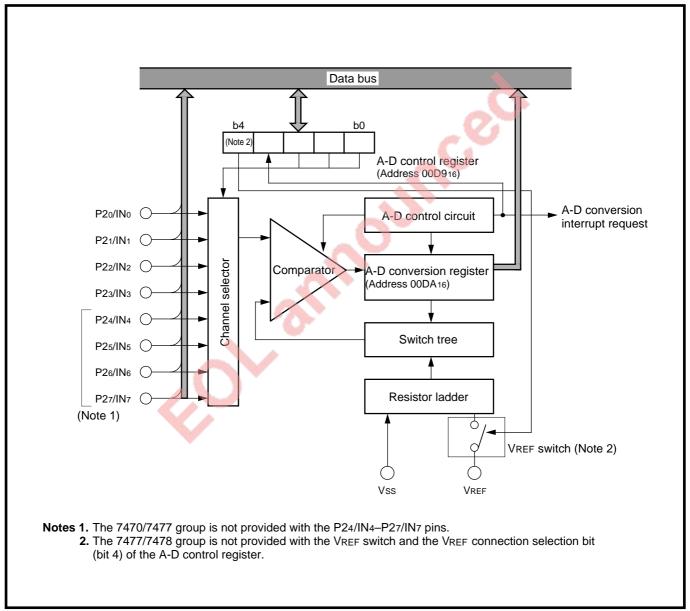

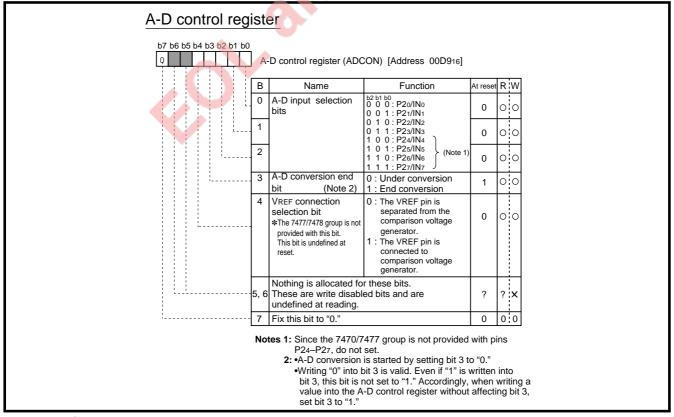

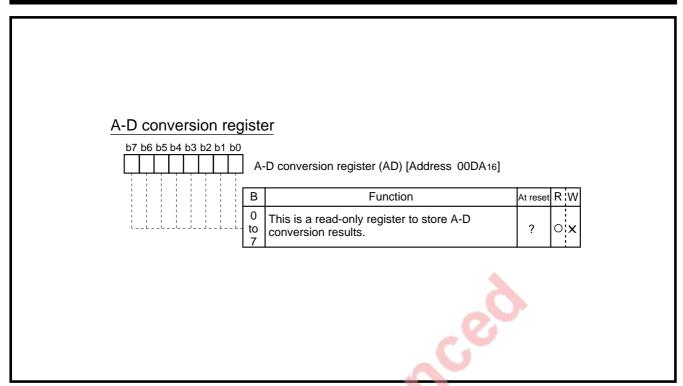

| 1.14 | A-D converter                                          | 1-139 |

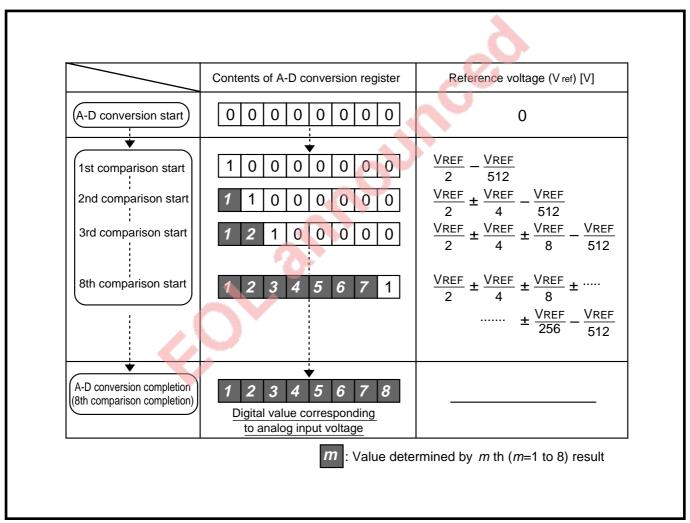

|      | 1.14.1 A-D conversion method                           | 1-140 |

|      | 1.14.2 Pins                                            | 1-144 |

|      | 1.14.3 Notes on use                                    | 1-144 |

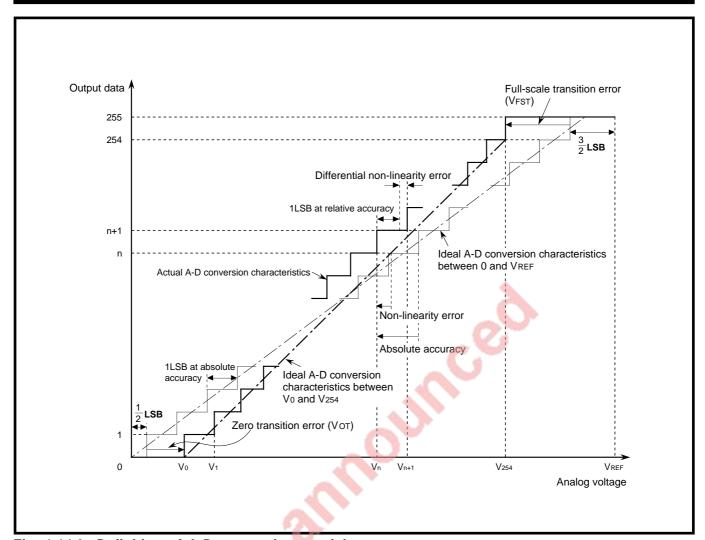

|      | 1.14.4 References                                      |       |

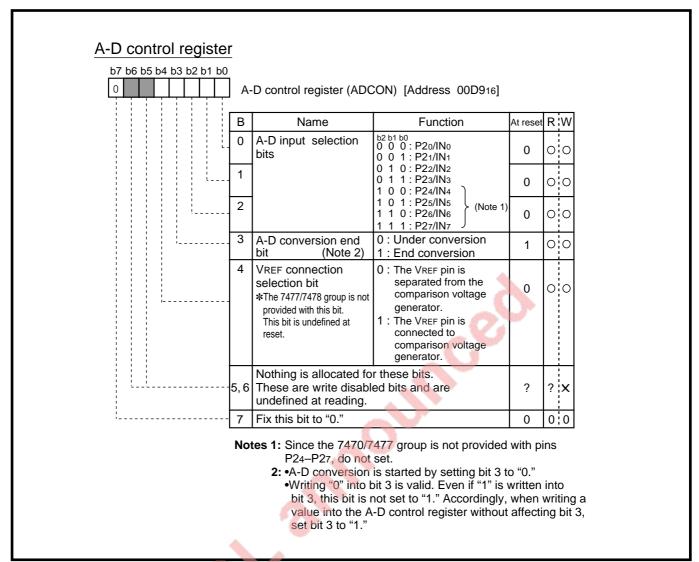

|      | 1.14.5 Related registers                               | 1-147 |

| 1.15 | Reset                                                  |       |

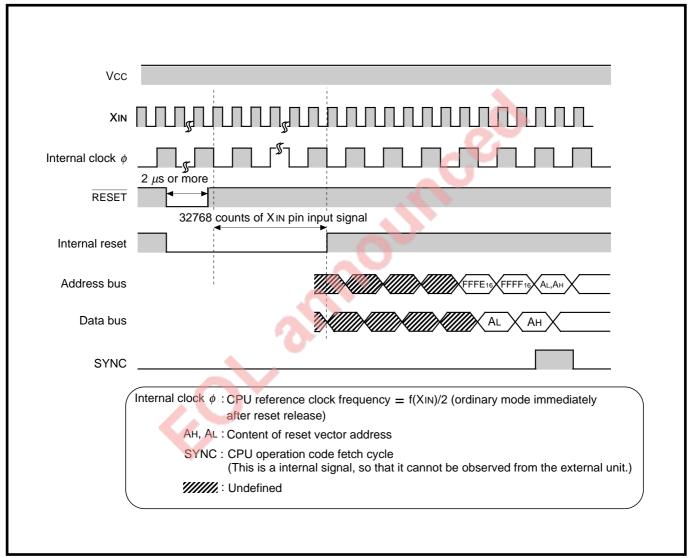

|      | 1.15.1 Operation description                           | 1-149 |

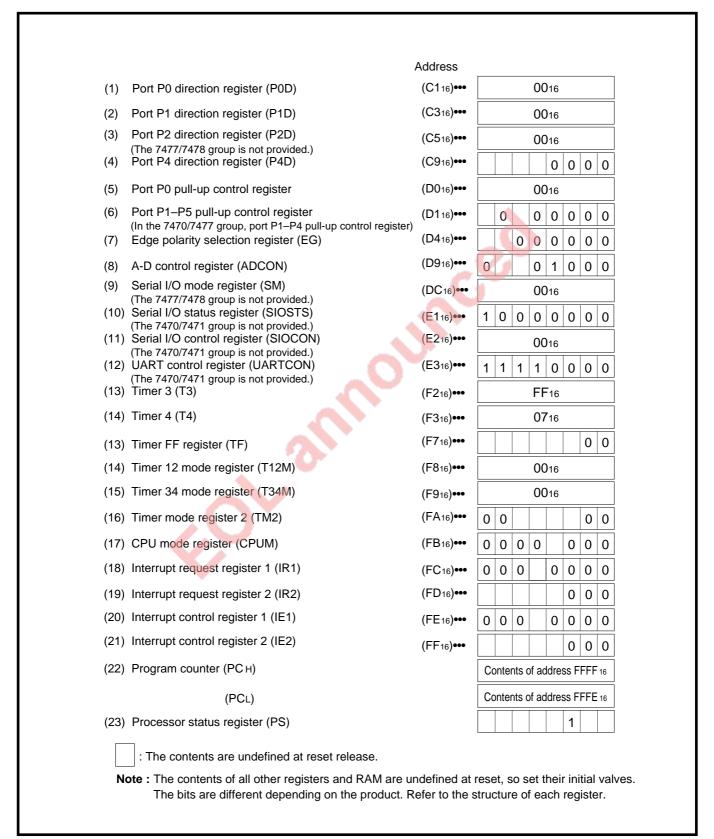

|      | 1.15.2 Internal status immediately after reset release |       |

|      | 1.15.3 Notes on use                                    |       |

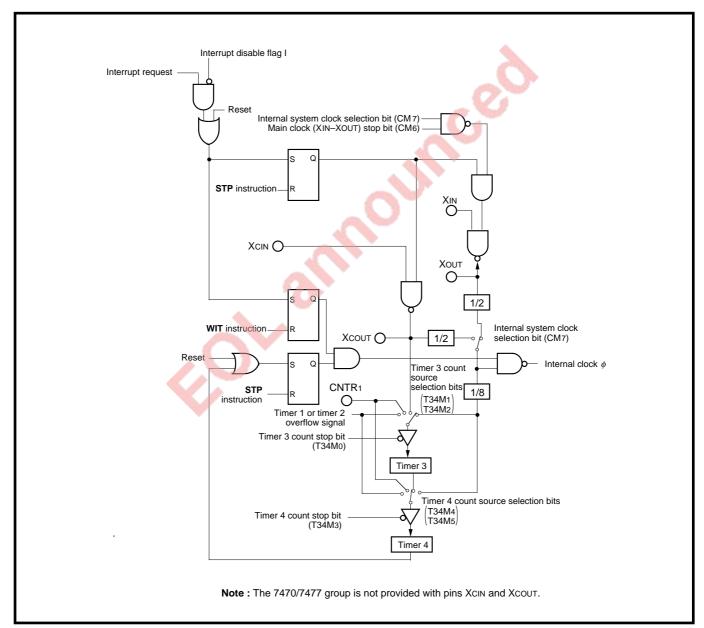

| 1.16 | Oscillation circuit                                    |       |

|      | 1.16.1 Oscillation circuit                             | 1-153 |

|      | 1.16.2 Sub-clock oscillation circuit                   |       |

|      | 1.16.3 Oscillation operation                           | 1-156 |

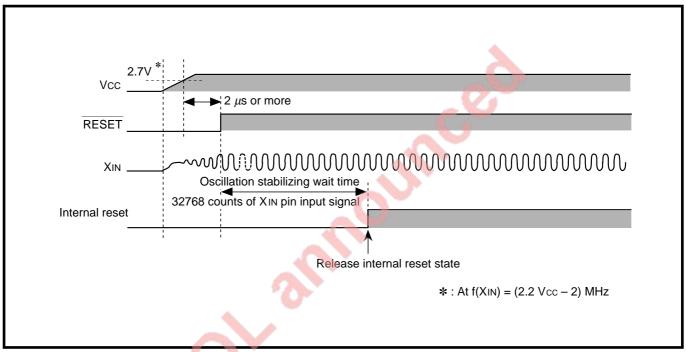

|      | 1.16.4 Oscillation stabilizing time                    | 1-158 |

|      | 1.16.5 Notes on use                                    | 1-159 |

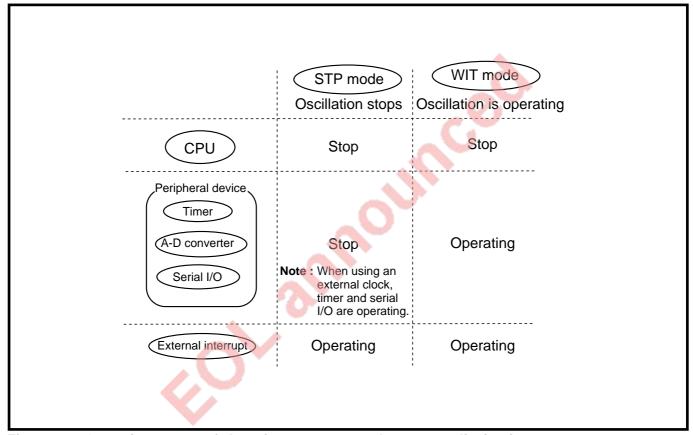

| 1.17 | Low-power dissipation function                         | 1-160 |

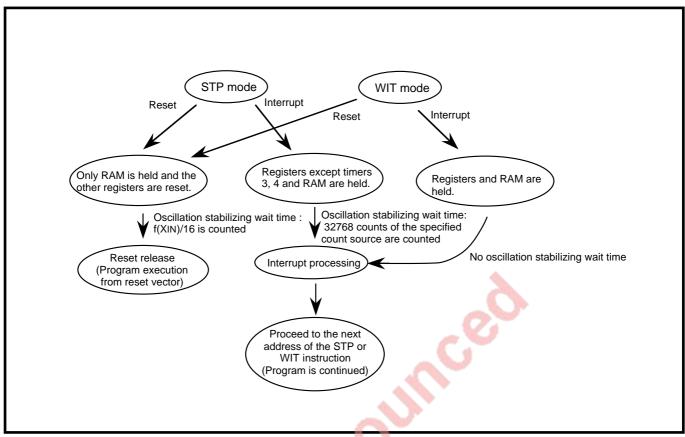

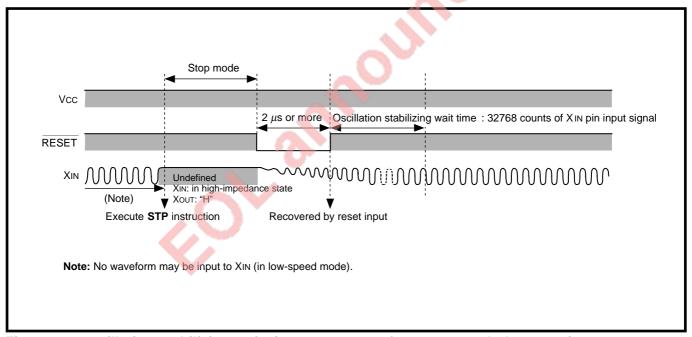

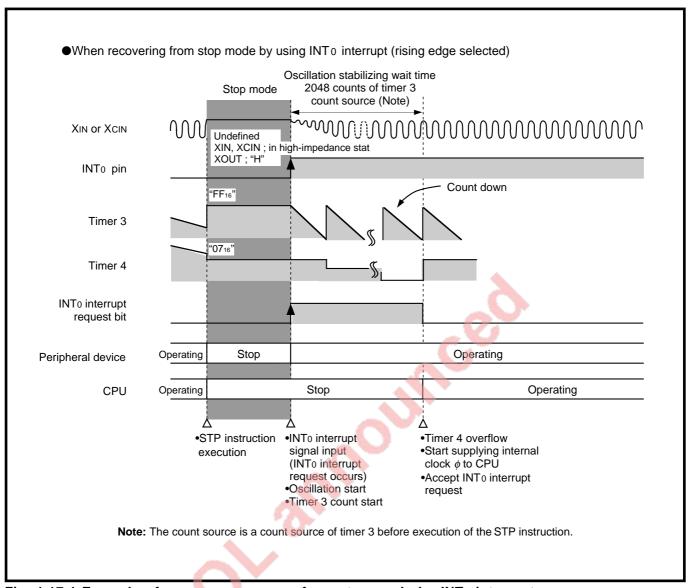

|      | 1.17.1 Stop mode                                       | 1-162 |

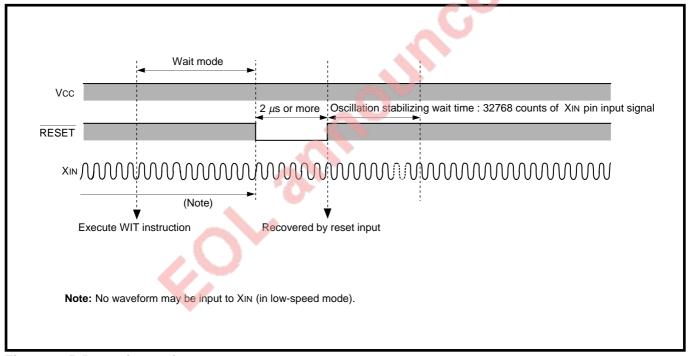

|      | 1.17.2 Wait mode                                       | 1-166 |

|      | 1.17.3 Notes on use                                    | 1-169 |

|      | 1.17.4 Related register                                | 1-170 |

| 1.18 | State transitions                                      | 1-171 |

| 1.19 | Built-in PROM version                                  | 1-175 |

|      | 1.19.1 EPROM mode                                      | 1-176 |

|      | 1.19.2 Pin description                                 | 1-182 |

|      | 1.19.3 Writing, reading, and erasing to built-in PROM  | 1-185 |

|      | 1.19.4 Notes on use                                    | 1-186 |

| 1.20 | Emulator MCU                                           | 1-188 |

| 1.21 | Electrical characteristics                             | 1-189 |

|      | 1.21.1 Electrical characteristics                      | 1-189 |

|      | 1.21.2 Timing requirements, switching characteristics  | 1-201 |

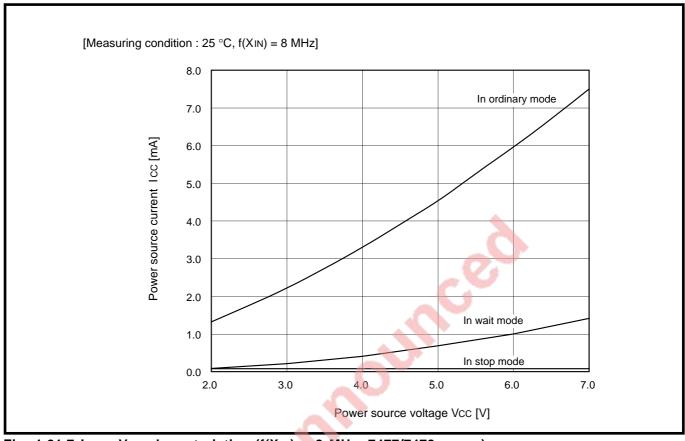

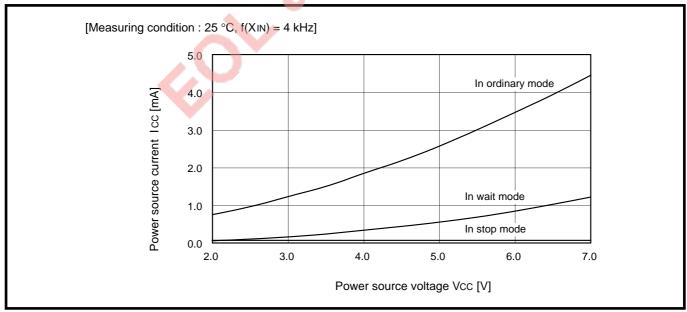

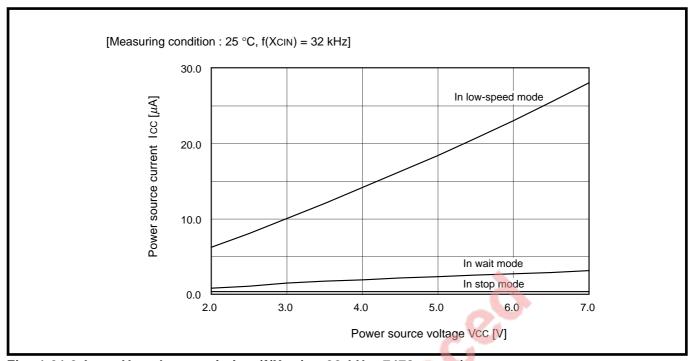

|      | 1.21.3 Power source current standard characteristics   | 1-203 |

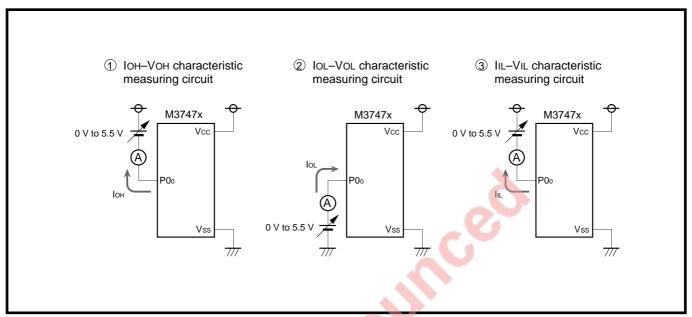

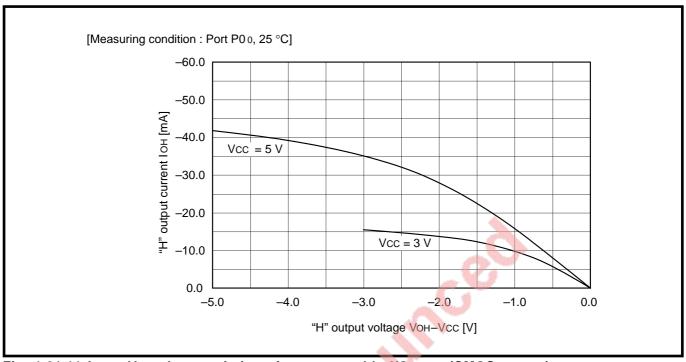

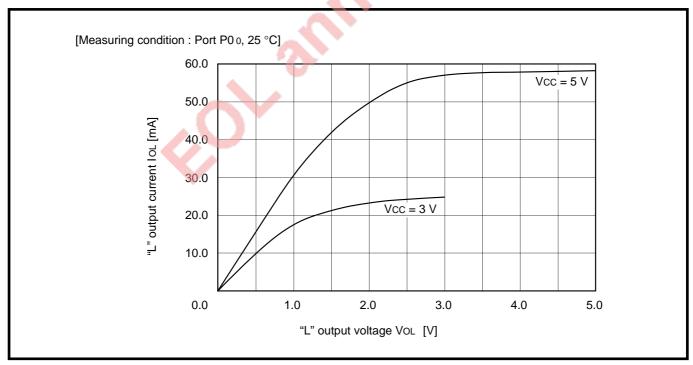

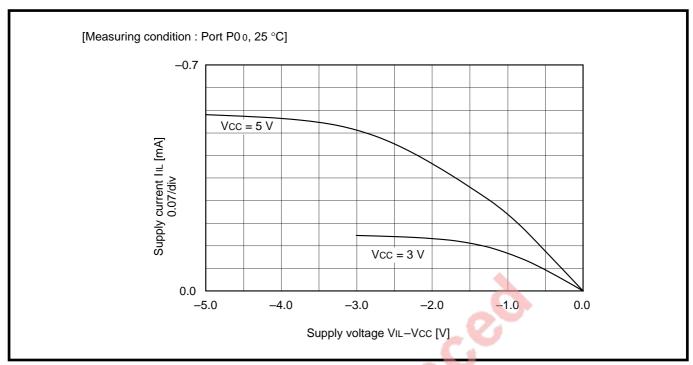

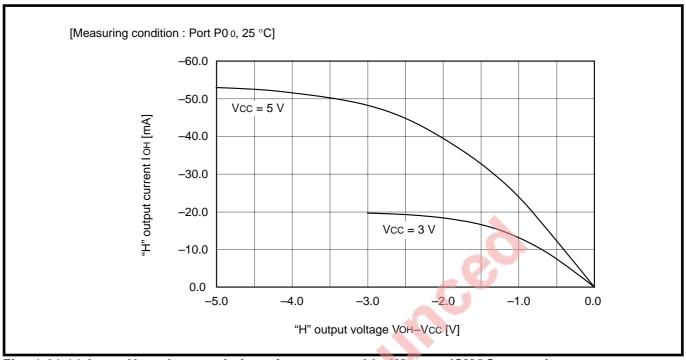

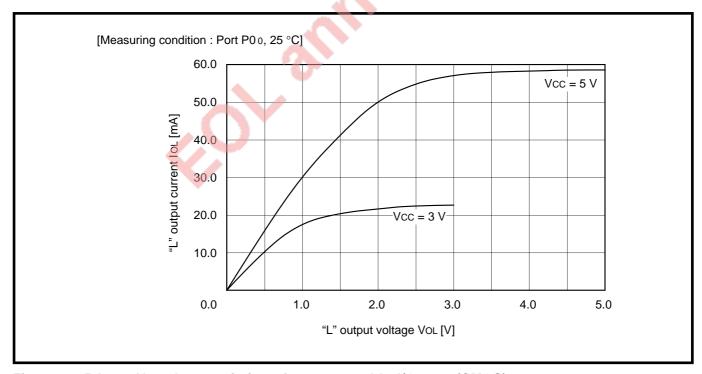

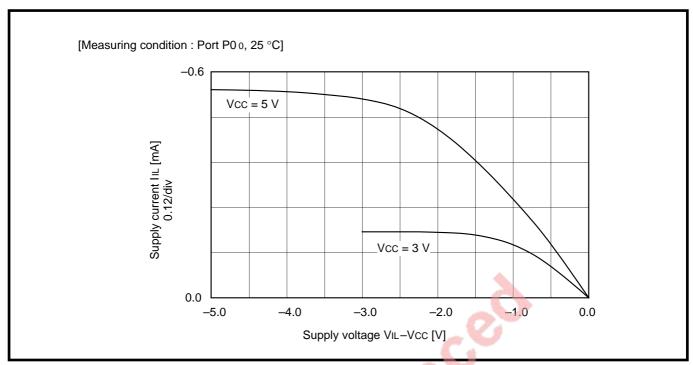

|      | 1.21.4 Port standard characteristics                   | 1-208 |

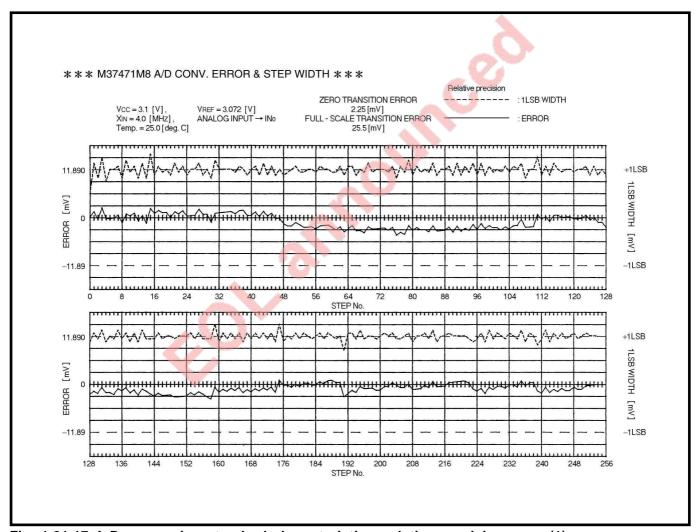

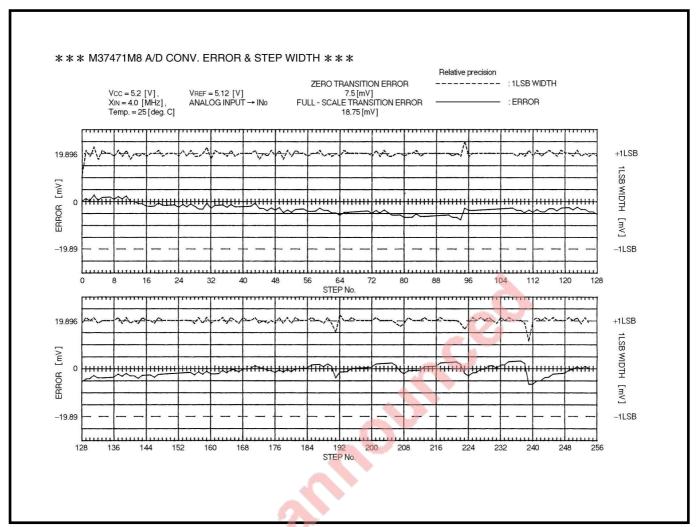

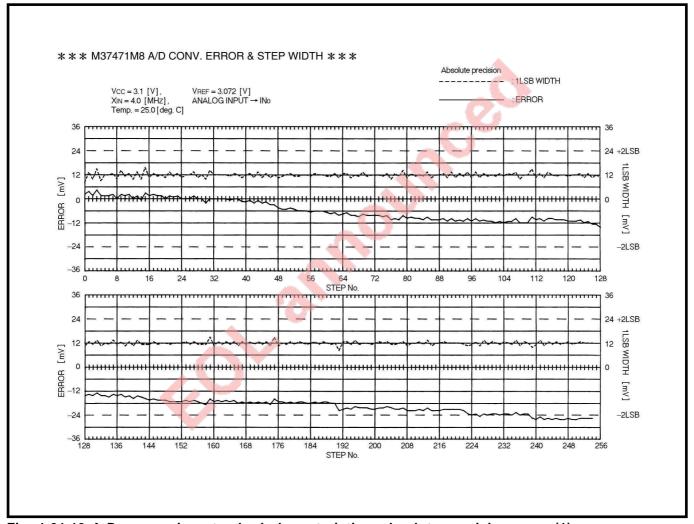

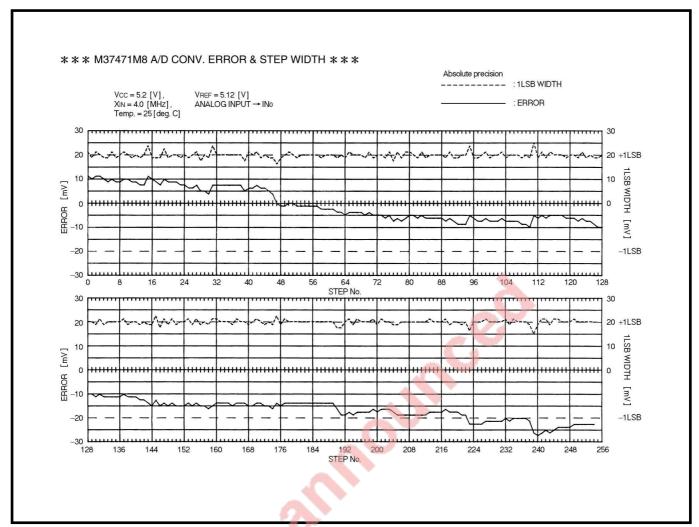

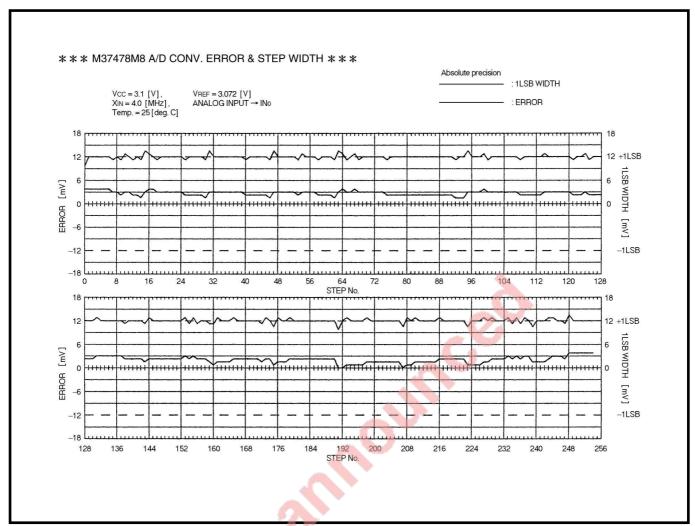

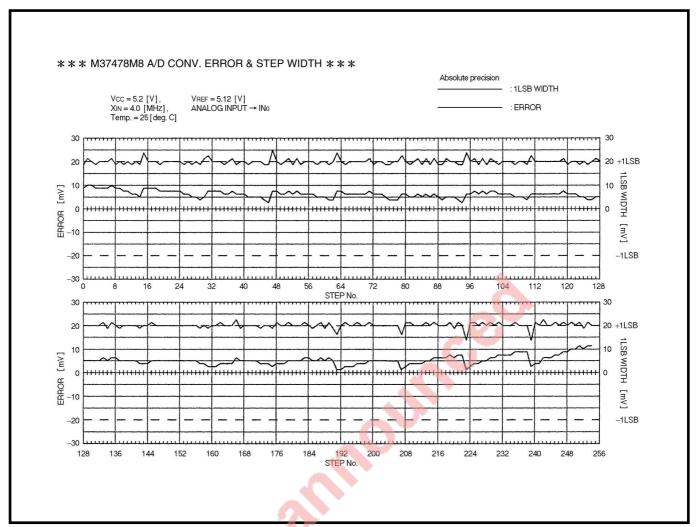

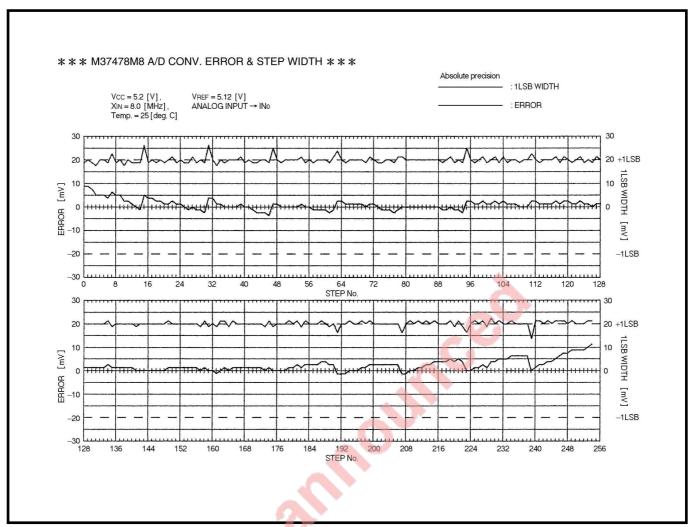

|      | 1.21.5 A-D conversion standard characteristics         | 1-213 |

# CHAPTER 2. APPLICATION

| 2.1  | I/O pins                                                                    | 2-2  |

|------|-----------------------------------------------------------------------------|------|

|      | 2.1.1 I/O port                                                              | 2-2  |

|      | 2.1.2 Notes on use                                                          | 2-5  |

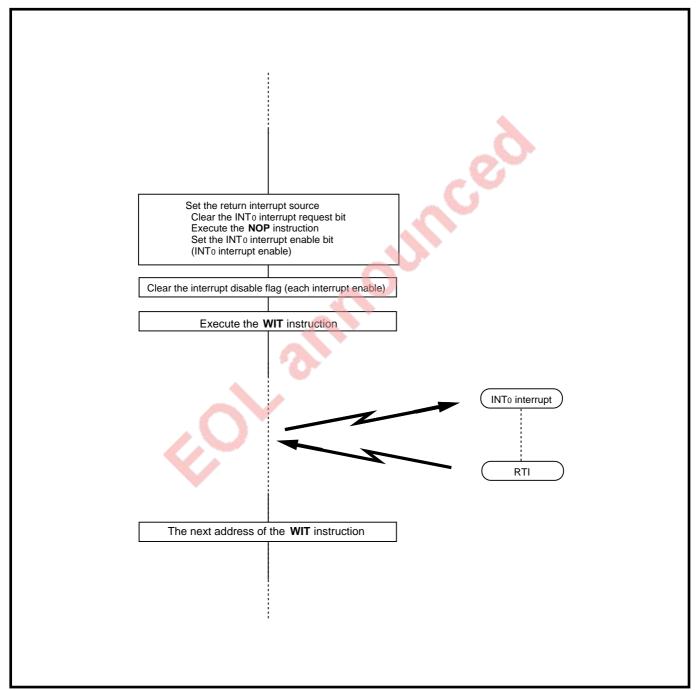

| 2.2  | Interrupts                                                                  | 2-7  |

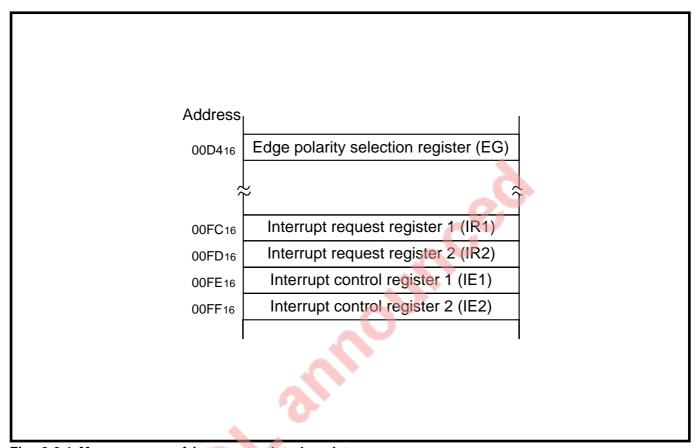

|      | 2.2.1 Memory allocation                                                     | 2-7  |

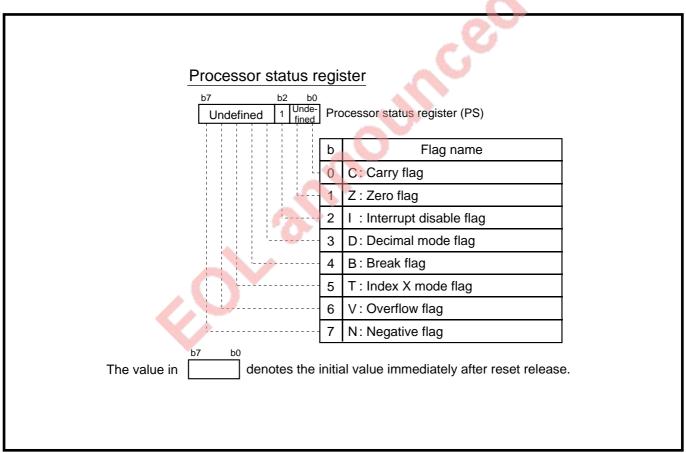

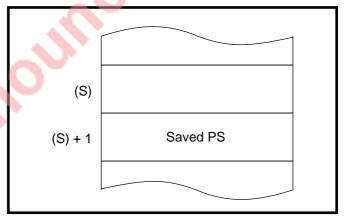

|      | 2.2.2 Processor status register (PS)                                        | 2-8  |

|      | 2.2.3 Application example                                                   | 2-9  |

|      | 2.2.4 Notes on use                                                          | 2-9  |

| 2.3  | Timers                                                                      | 2-10 |

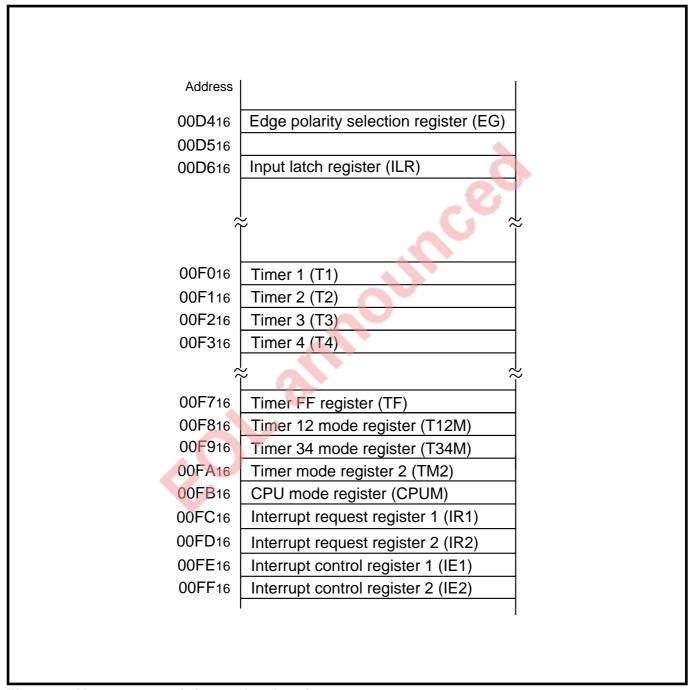

|      | 2.3.1 Memory allocation                                                     | 2-10 |

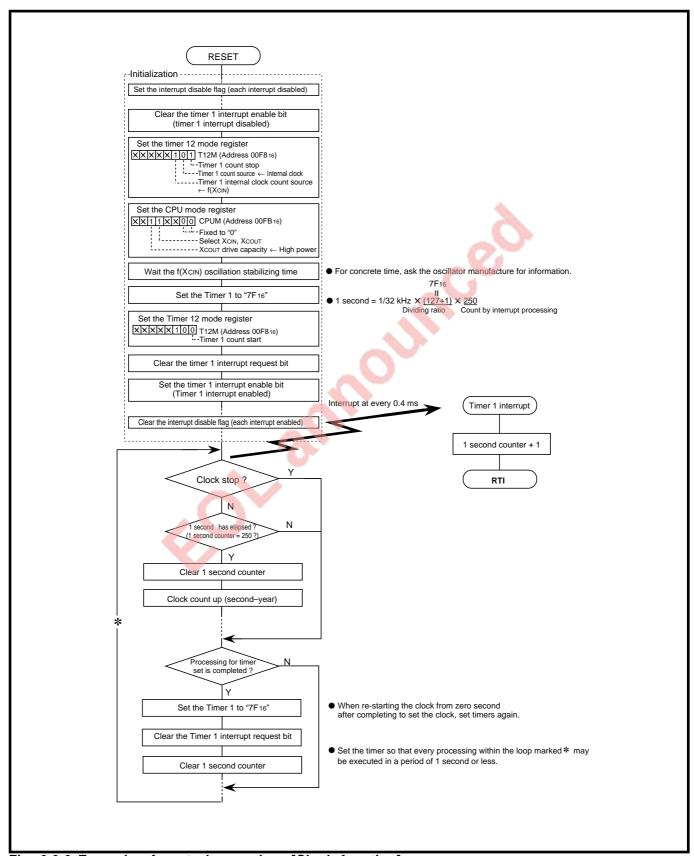

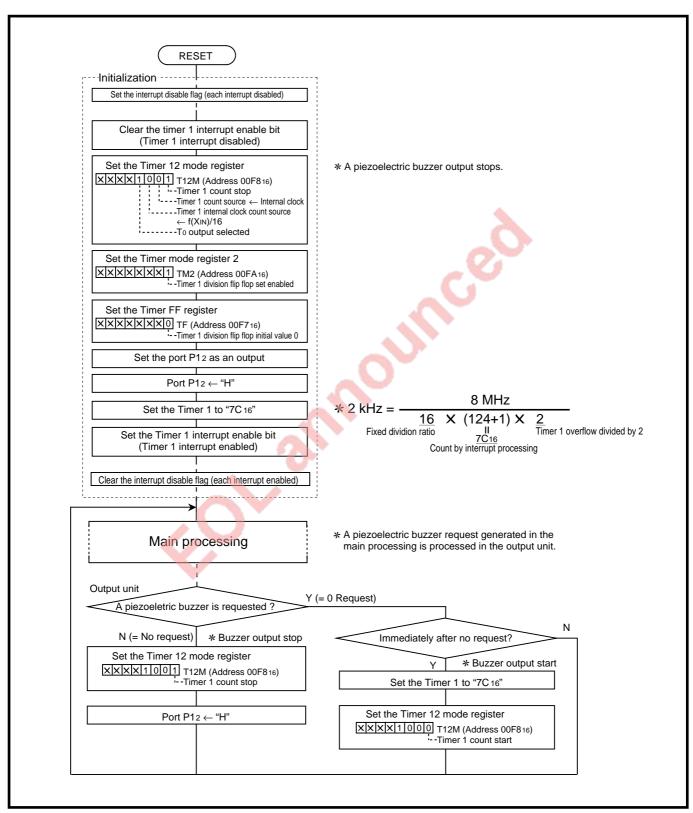

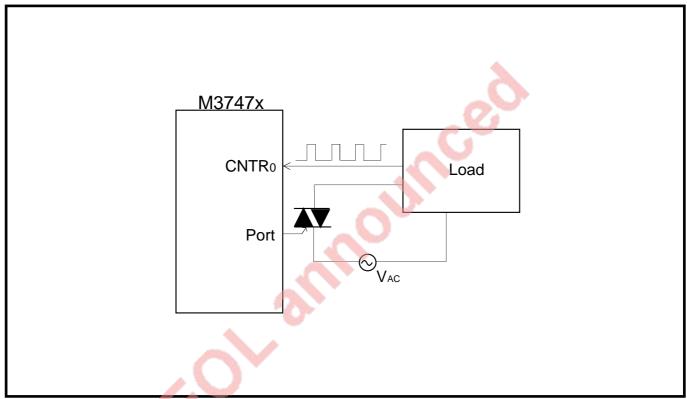

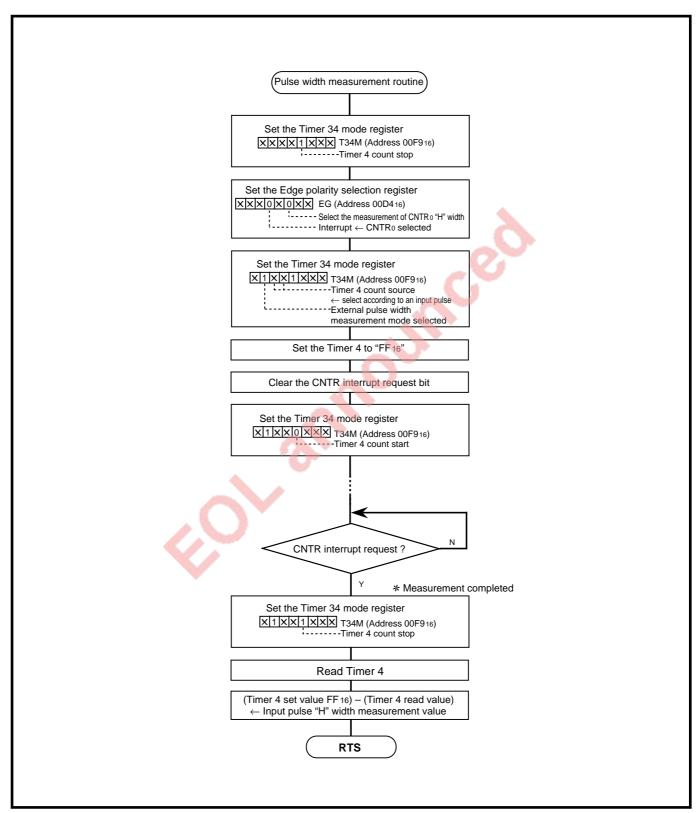

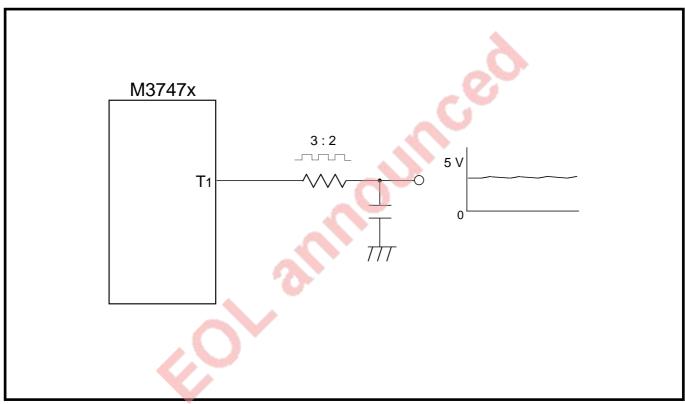

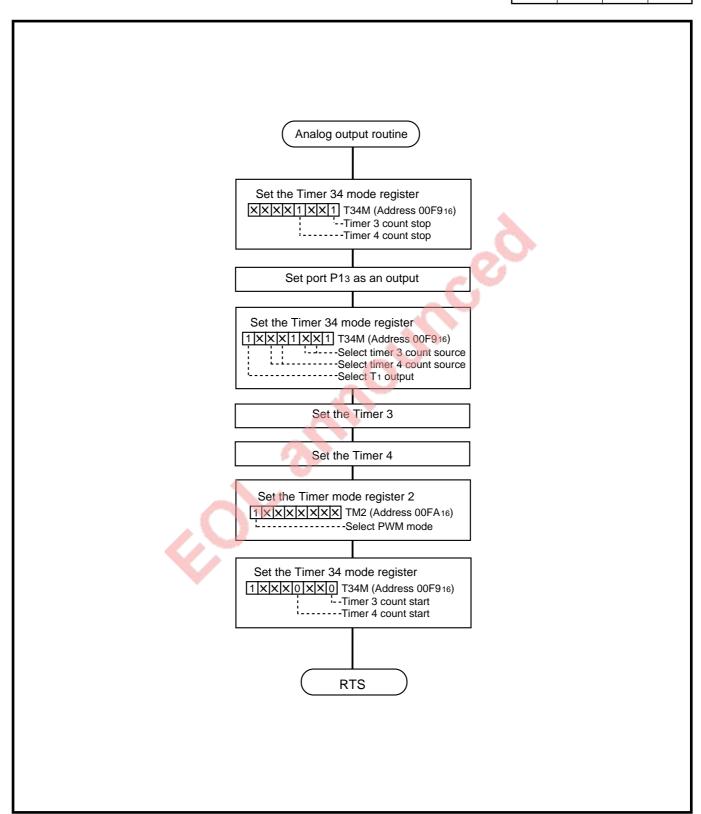

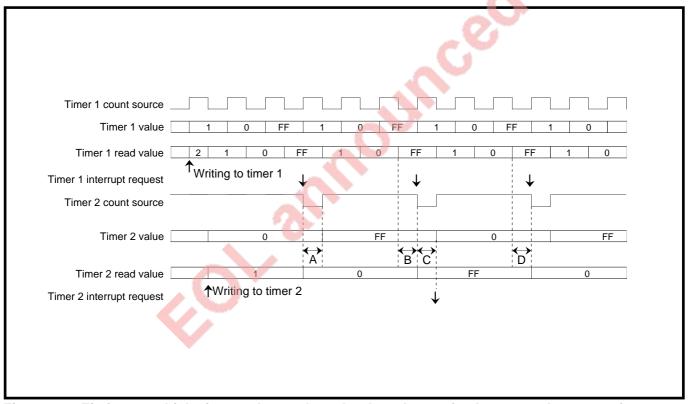

|      | 2.3.2 Application example                                                   | 2-11 |

|      | 2.3.3 Notes on use                                                          | 2-22 |

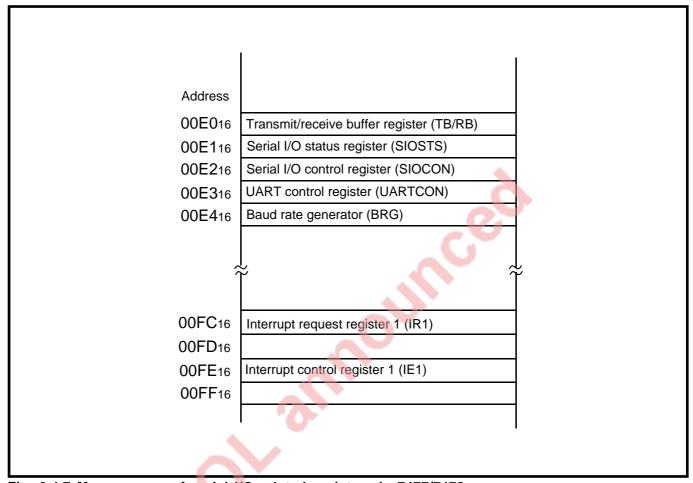

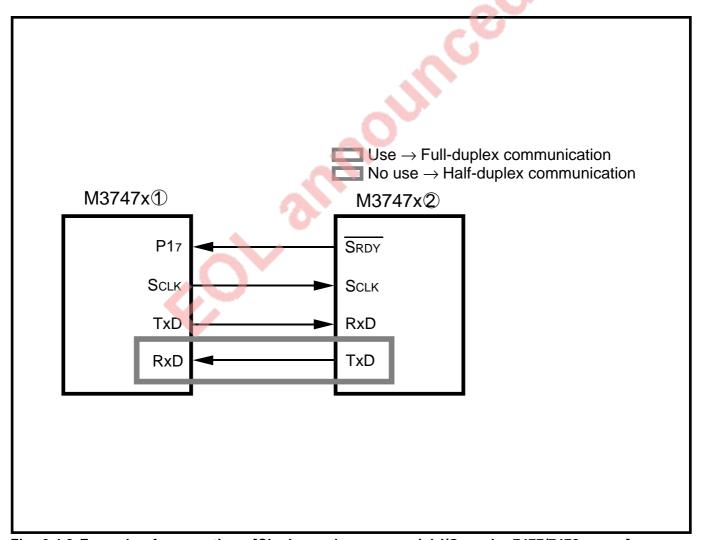

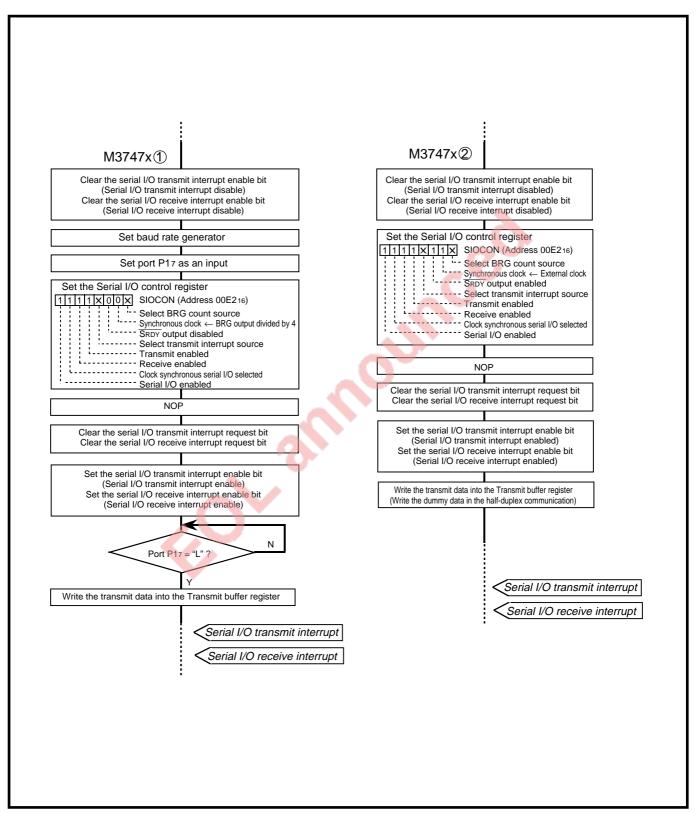

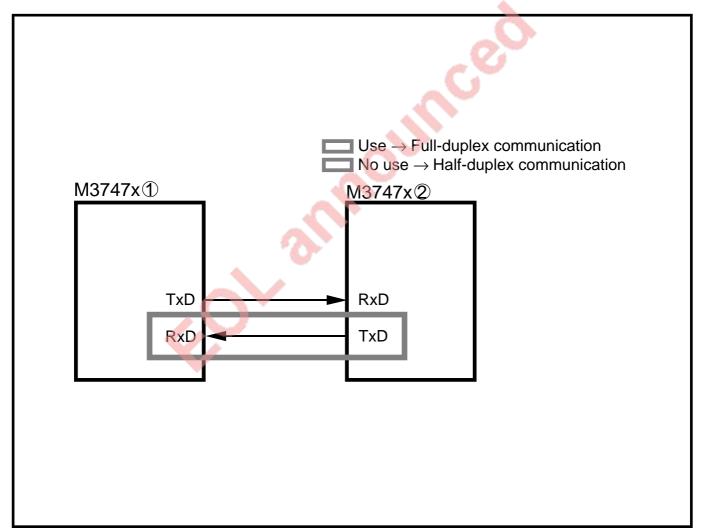

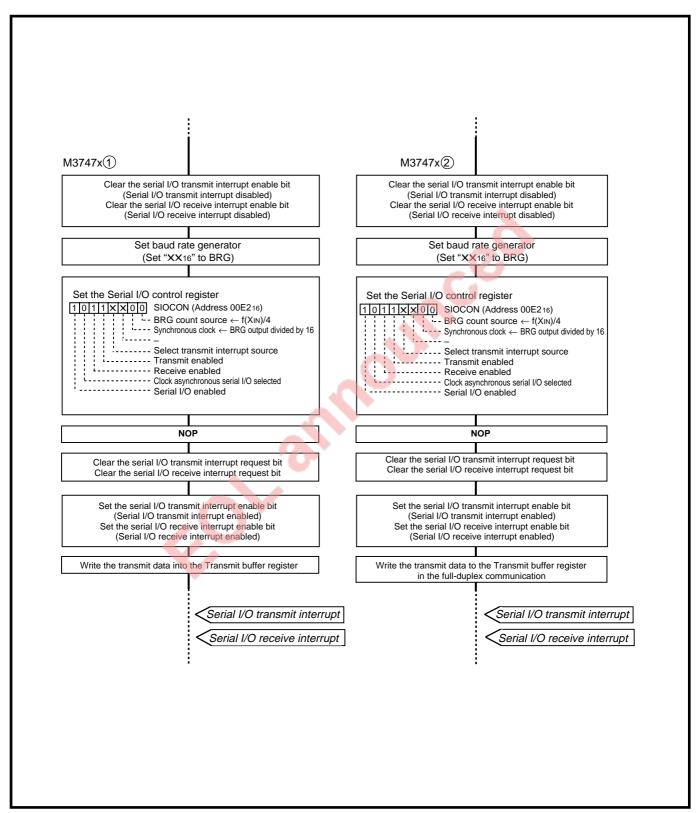

| 2.4  | Serial I/O                                                                  | 2-23 |

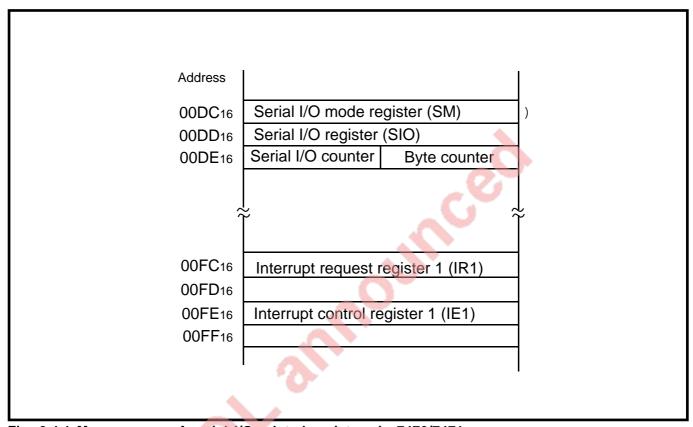

|      | 2.4.1 7470/7471 group memory allocation                                     |      |

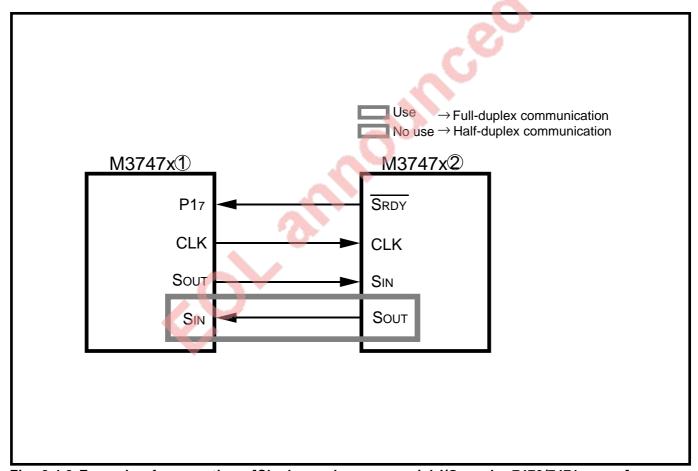

|      | 2.4.2 Application example                                                   | 2-24 |

|      | 2.4.3 7477/7478 group memory allocation                                     | 2-29 |

|      | 2.4.4 Application examples                                                  |      |

|      | 2.4.5 Notes on use                                                          | 2-34 |

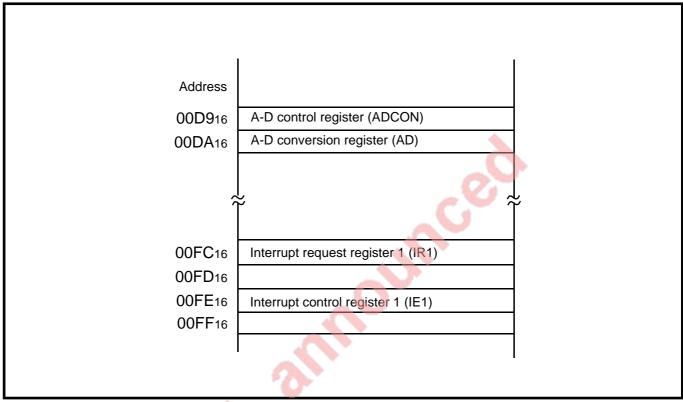

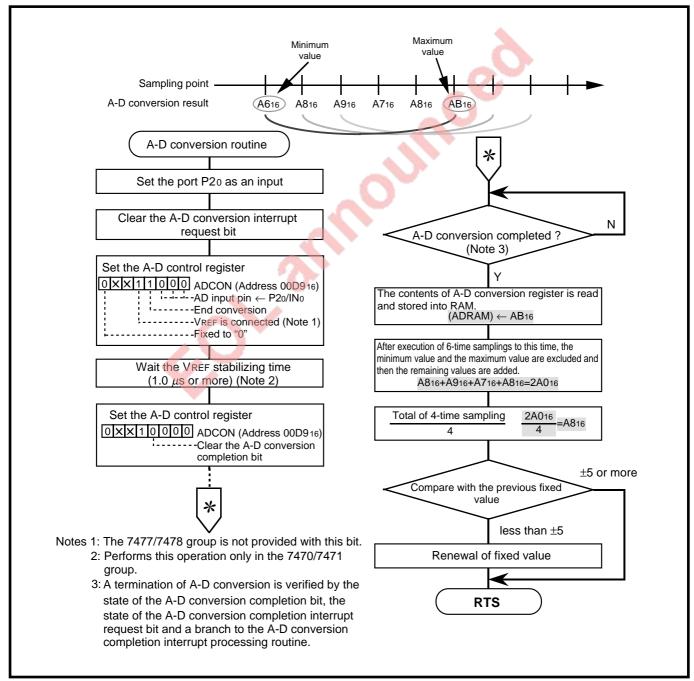

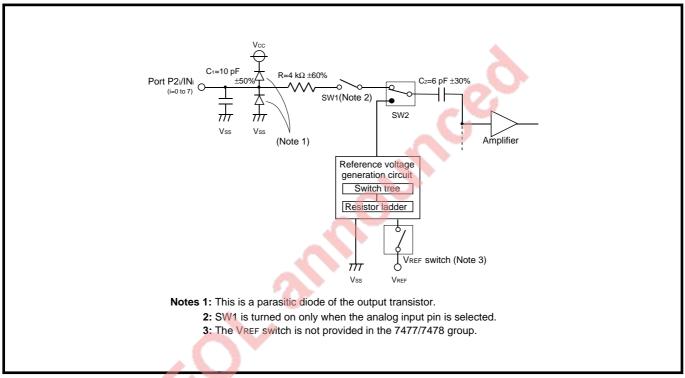

| 2.5  | A-D converter                                                               |      |

|      | 2.5.1 Memory allocation                                                     | 2-35 |

|      | 2.5.2 Application examples                                                  | 2-36 |

|      | 2.5.3 Notes on use                                                          | 2-38 |

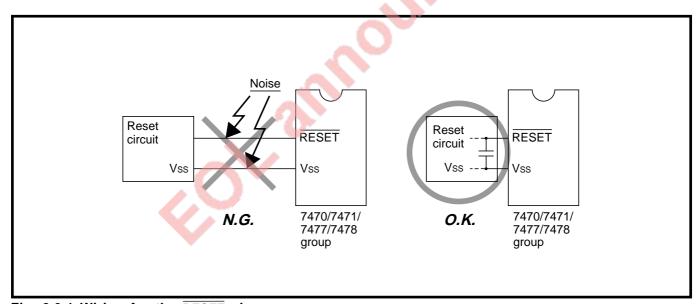

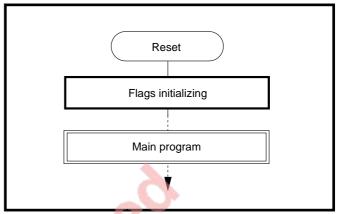

| 2.6  | Reset                                                                       | 2-39 |

|      | 2.6.1 Reset circuit                                                         | 2-39 |

|      | 2.6.2 Notes on use                                                          | 2-39 |

| 2.7  | Oscillation circuit                                                         | 2-40 |

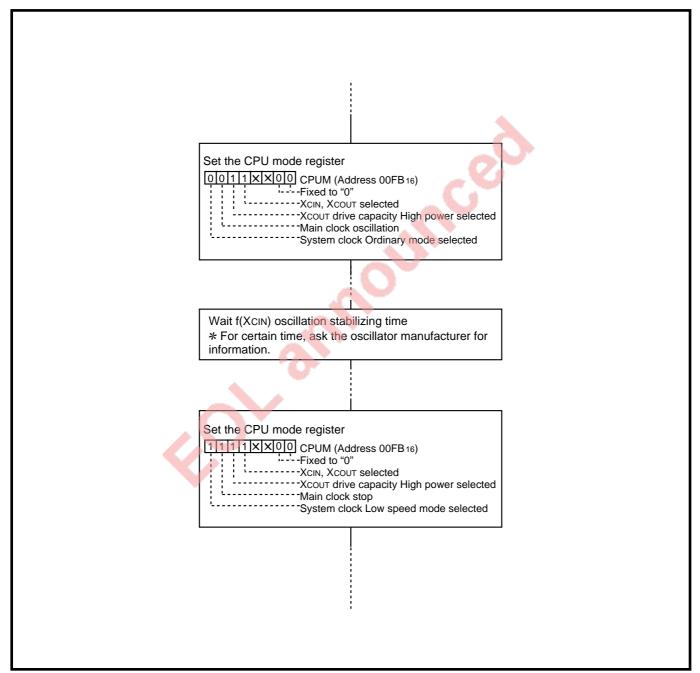

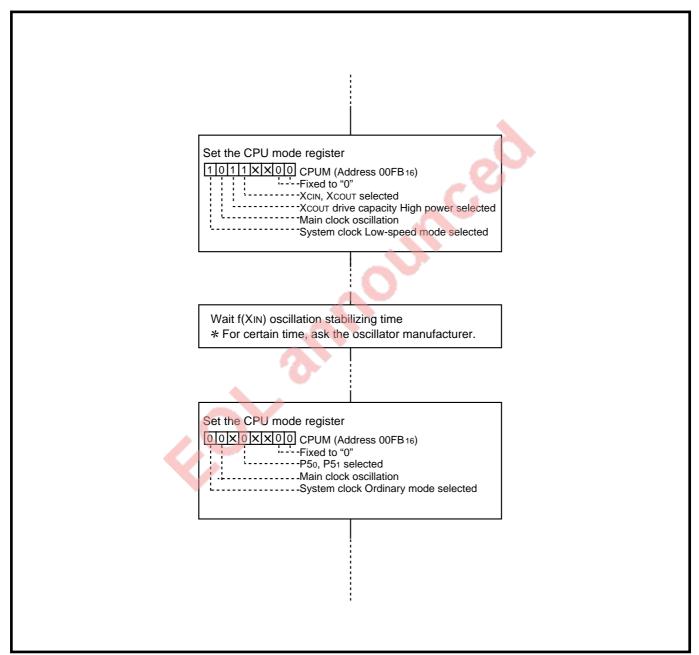

| 2.8  | Low-power dissipation function                                              | 2-41 |

|      | 2.8.1 CPU mode register                                                     | 2-41 |

|      | 2.8.2 Application examples                                                  | 2-42 |

|      | 2.8.3 Notes on use                                                          | 2-47 |

| 2.9  | Countermeasures against noise                                               | 2-48 |

|      | 2.9.1 Shortest wiring length                                                | 2-48 |

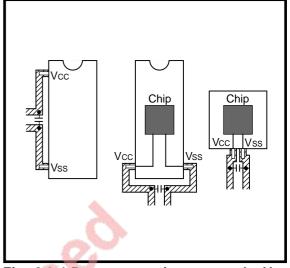

|      | 2.9.2 Connection of a bypass capacitor across the Vss line and the Vcc line | 2-51 |

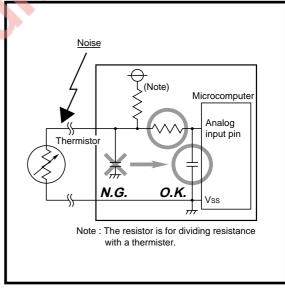

|      | 2.9.3 Wiring to analog input pins                                           | 2-51 |

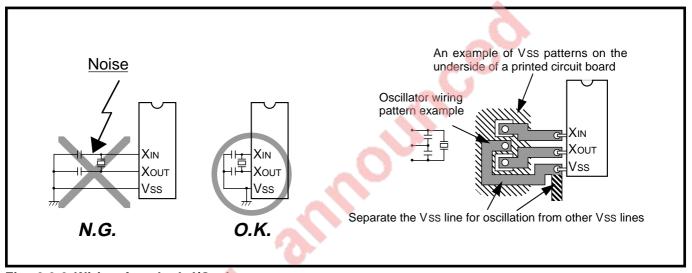

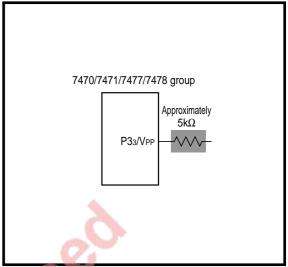

|      | 2.9.4 Consideration for oscillator                                          | 2-52 |

|      | 2.9.5 Setup for I/O ports                                                   | 2-53 |

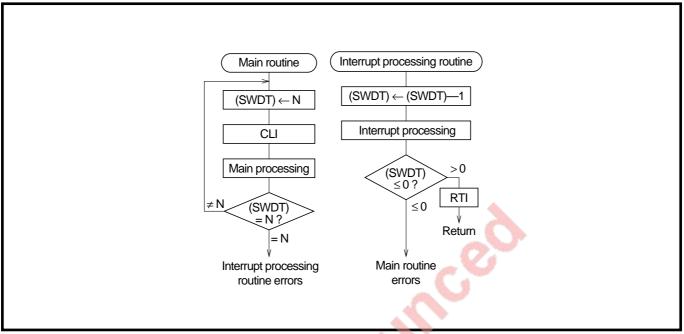

|      | 2.9.6 Providing of watchdog timer function by software                      | 2-54 |

| 2.10 | Notes on programming                                                        | 2-56 |

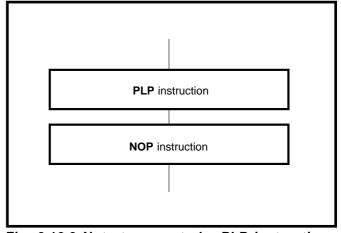

|      | 2.10.1 Processor status register                                            | 2-56 |

|      | 2.10.2 Decimal calculations                                                 | 2-57 |

| 2.11 | Differences between 7470/7471 group and 7477/7478 group                     | 2-58 |

#### Table of contents

| 2.      | 12 Example of application circuit | 2-59 |

|---------|-----------------------------------|------|

| CHAPTER | 3. APPENDIX                       |      |

| 3.      | 1 Control registers               | 3-2  |

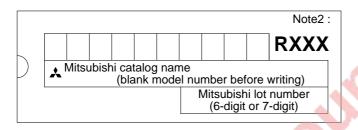

| 3.      | 2 Mask ROM ordering method        | 3-14 |

| 3.      | 3 ROM programming ordering method | 3-46 |

| 3.      | 4 Mark specification form         | 3-62 |

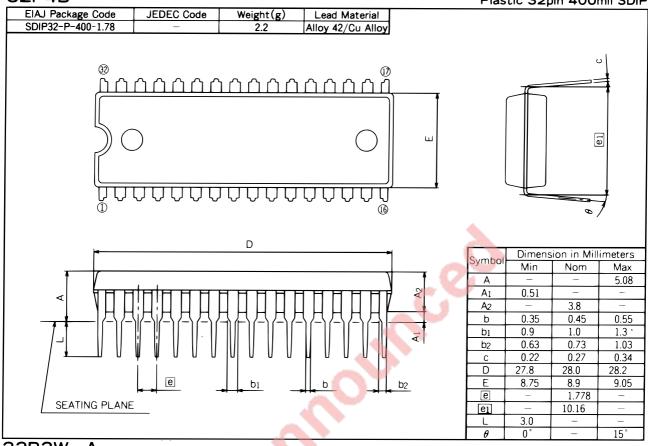

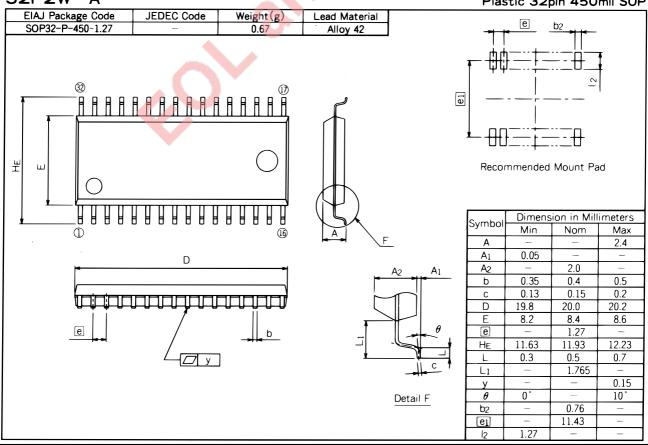

| 3.      | 5 Package outline                 | 3-67 |

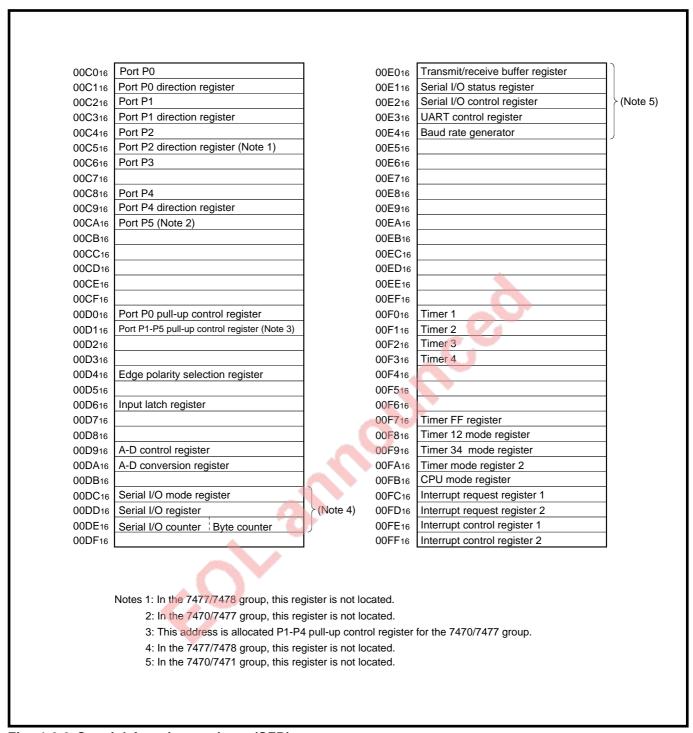

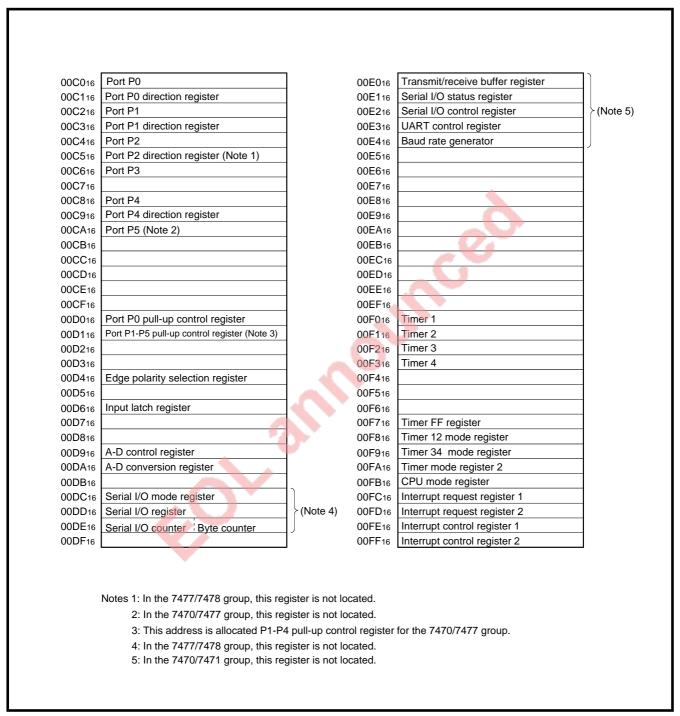

| 3.      | 6 SFR memory map                  | 3-69 |

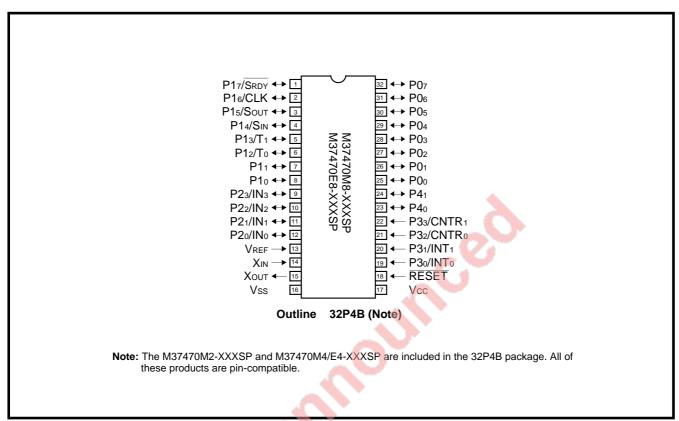

| 2       | 7 Din configuration               | 2.70 |

# CHAPTER 1

# **HARDWARE**

- 1.1 Description

- 1.2 Group expansion

- 1.3 Performance overview

- 1.4 Pin configuration

- 1.5 Pin description

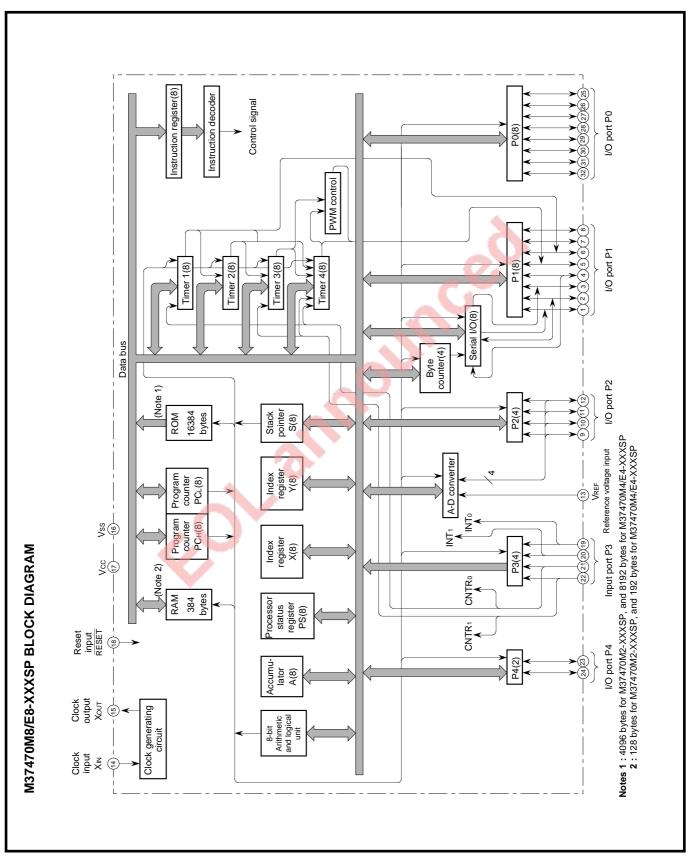

- 1.6 Functional block diagram

- 1.7 Central processing unit (CPU)

- 1.8 Access area

- 1.9 Memory allocation

- 1.10 I/O pins

- 1.11 Interrupts

- 1.12 Timers

- 1.13 Serial I/O

- 1.14 A-D converter

- 1.15 Reset

- 1.16 Oscillation circuit

- 1.17 Low-power dissipation function

- 1.18 State transitions

- 1.19 Built-in PROM version

- 1.20 Emulator MCU

- 1.21 Electrical characteristics

#### 1.1 Description

# 1.1 Description

The 7470/7471/7477/7478 group is an 8-bit single-chip microcomputer which utilizes a silicon gate CMOS processing and has a simple instruction system of the 740 family using the same memory space for ROM, RAM and I/O.

#### 1.2 Group expansion

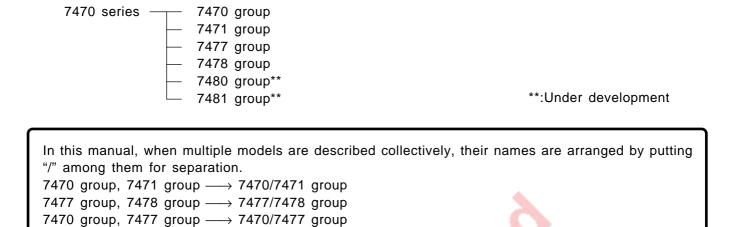

The 7470/7471/7477 group develops with the M37470M2-XXXSP as the base chip in the 7470 series. The classification of the 7470 series is as follows.

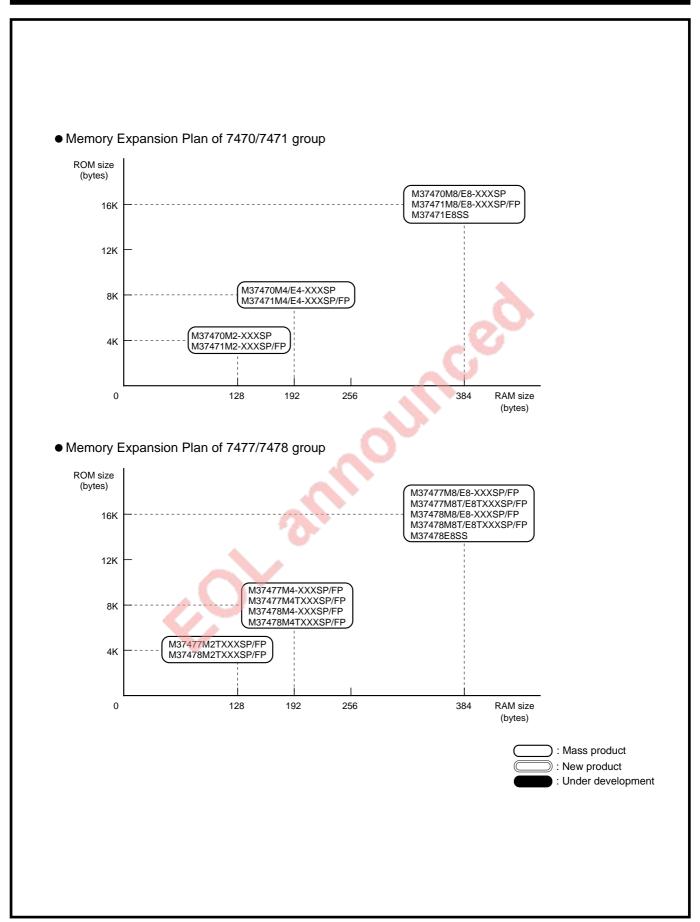

The 7470/7471/7477/7478 group permits group expansion as shown in Figure 1.2.1. This group expansion is all performed only by differences in memory type and capacity and the number of ports. This allows the user to select optimum elements according to the user's system.

The 7470/7471/7477/7478 group supports the following in addition to the mask ROM version.

#### (1) Support of One Time PROM version

7471 group, 7478 group ----- 7471/7478 group

The One Time PROM version is a programmable microcomputer and can perform a one-time write operation to the built-in programmable ROM (PROM).

For the details, refer to "1.19 Built-in PROM version."

#### (2) Support of EPROM version (with window)

The built-in EPROM version is a programmable microcomputer with window and can perform write and erase operations to the built-in EPROM.

For the details, refer to "1.19 Built-in PROM version."

#### (3) Support of emulator MCU

The emulator MCU is a microcomputer designed for program development which facilitates program development and is an optimum element for system evaluation.

For the details, refer to "1.20 Emulator MCU."

Table 1.2.1 shows the products which the 7470/7471/7477/7478 group supports.

#### 1.2 Group expansion

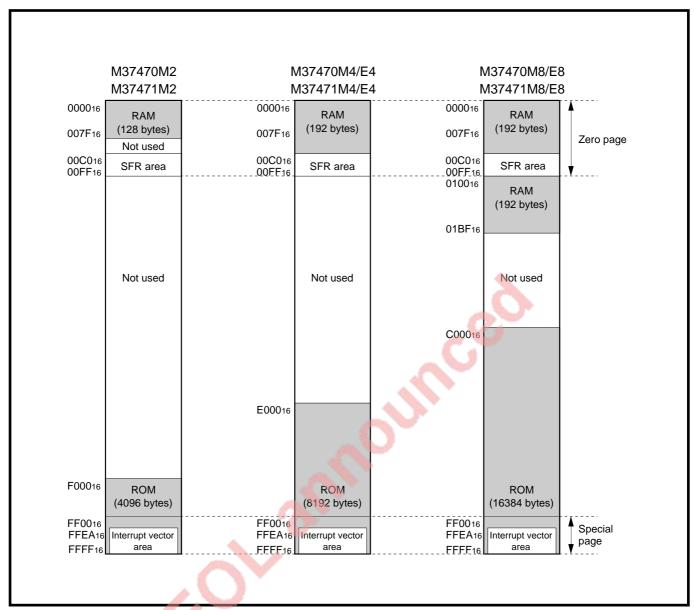

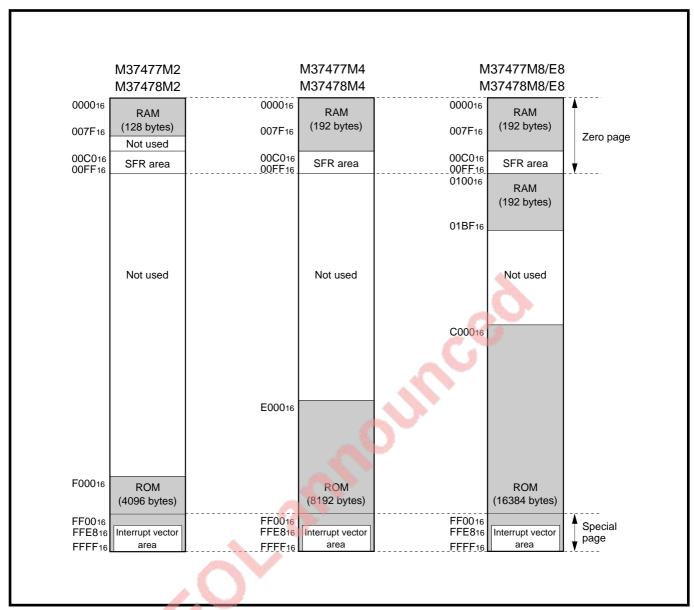

Fig. 1.2.1 Memory expansion plan of 7470/7471/7477/7478 group

(As of July 1996)

# 1.2 Group expansion

Table 1.2.1 List of supported products

(As of July 1996)

| Product        | ROM<br>(bytes)  | RAM<br>(bytes) | I/O Port                         | Package | Remarks                |

|----------------|-----------------|----------------|----------------------------------|---------|------------------------|

| M37470M2-XXXSP | 4096            | 128            | 1/O norto: 22                    |         | Mari DOM andre         |

| M37470M4-XXXSP |                 |                | I/O ports: 22                    |         | Mask ROM version       |

| M37470E4-XXXSP | 8192            | 192            | (Including 4 analog              | 32P4B   | One Time PROM version  |

| M37470M8-XXXSP |                 |                | input pins.)                     | 021 40  | Mask ROM version       |

| M37470E8-XXXSP | 16384           | 384            | Input ports: 4                   |         | One Time PROM version  |

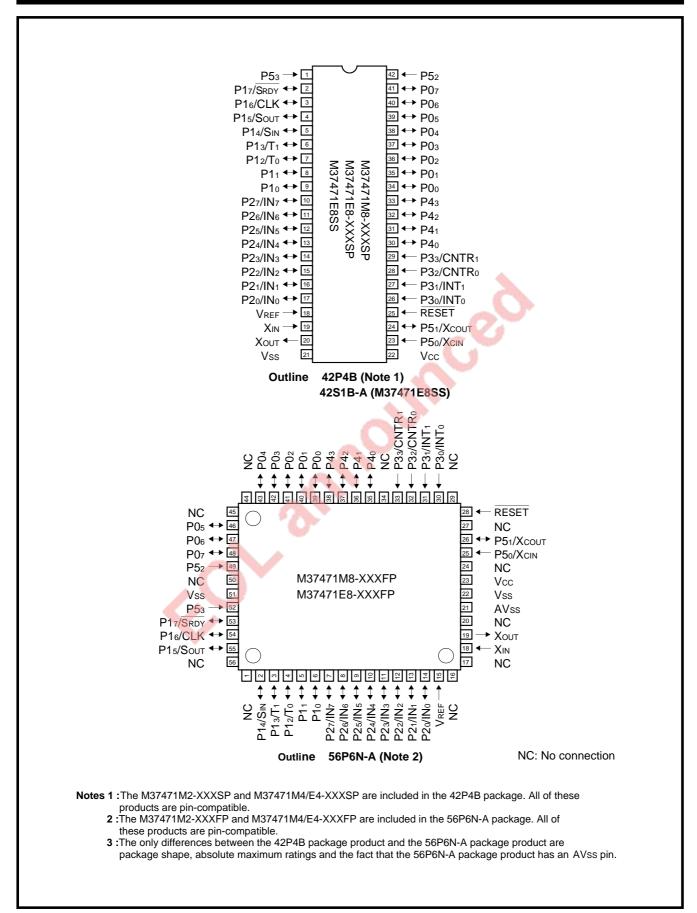

| M37471M2-XXXSP |                 |                |                                  | 42P4B   |                        |

| M37471M2-XXXFP | 4096            | 128            |                                  | 56P6N-A |                        |

| M37471M4-XXXSP |                 |                |                                  | 42P4B   | Mask ROM version       |

| M37471M4-XXXFP |                 |                |                                  | 56P6N-A |                        |

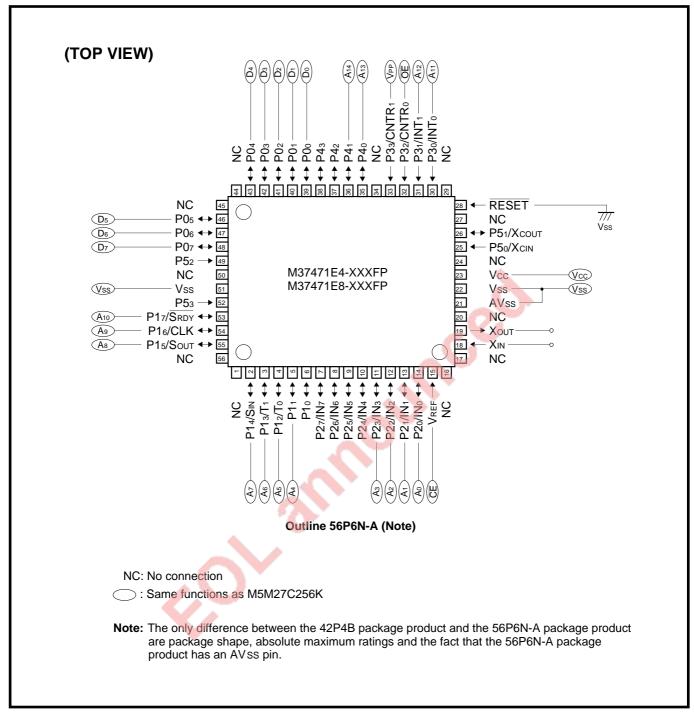

| M37471E4-XXXSP | 8192            | 192            | 1/0                              | 42P4B   |                        |

| M37471E4-XXXFP |                 |                | I/O ports: 28                    | 56P6N-A | One Time PROM version  |

| M37471M8-XXXIP |                 |                | (Including 8 analog              | 42P4B   |                        |

| M37471M8-XXXFP |                 |                | input pins.)                     | 56P6N-A | Mask ROM version       |

|                | 16384           | 384            | Input ports: 8                   | 42P4B   |                        |

| M37471E8-XXXSP | 10304           | 304            |                                  |         | One Time PROM version  |

| M37471E8-XXXFP |                 |                |                                  | 56P6N-A | EDDOM version          |

| M37471E8SS     | 00.514          |                |                                  | 42S1B-A | EPROM version          |

| M37471RSS      | 63.5K<br>(Note) | 384            |                                  | 42S1M   | Emulator MCU           |

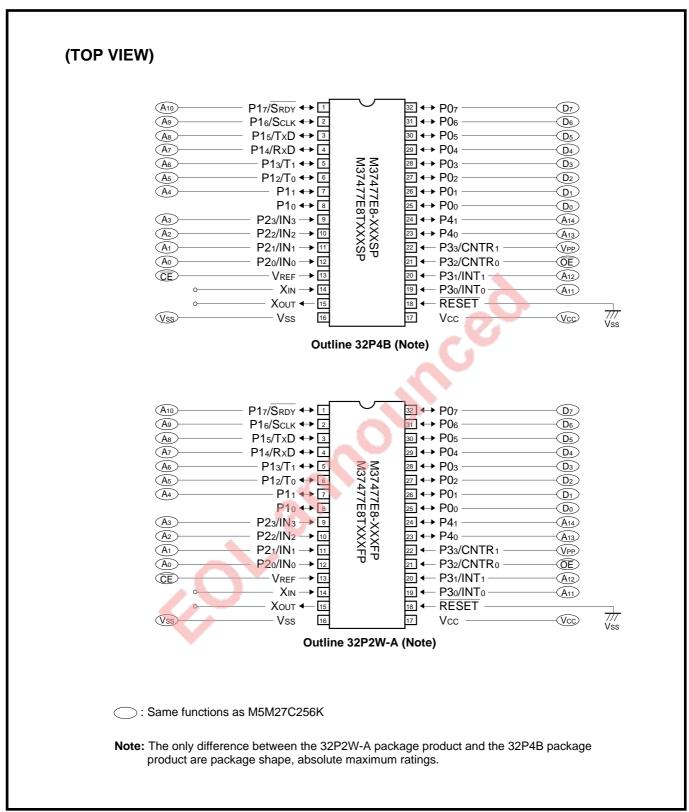

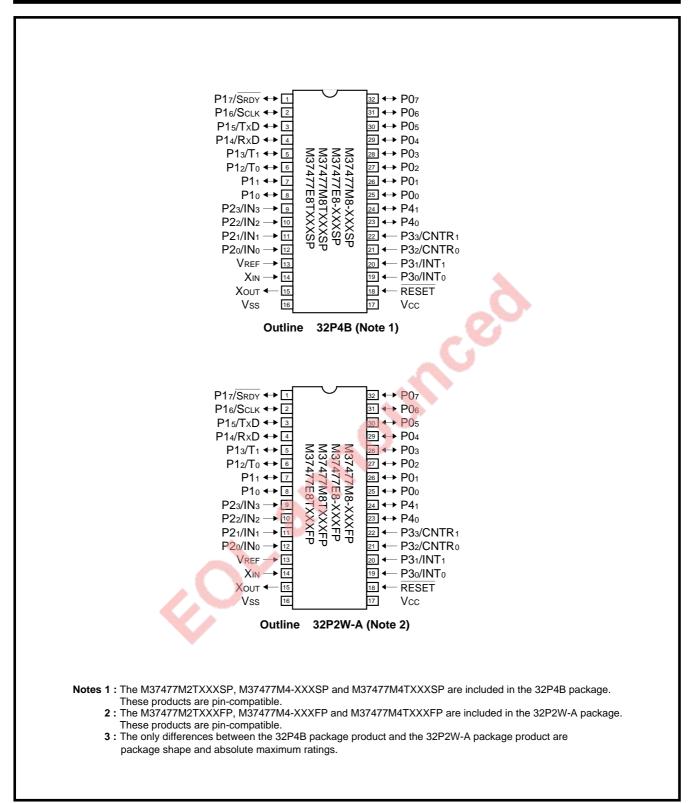

| M37477M2TXXXSP | 4096            | 128            |                                  | 32P4B   | Mask ROM version*      |

| M37477M2TXXXFP | 4000            | 120            |                                  | 32P2W-A | Wask Kow Version       |

| M37477M4-XXXSP |                 |                |                                  | 32P4B   | Mask ROM version       |

| M37477M4-XXXFP | 8192            | 192            |                                  | 32P2W-A | Wask Kow Version       |

| M37477M4TXXXSP | 0192            | 192            | I/O ports: 18                    | 32P4B   | Mask ROM version*      |

| M37477M4TXXXFP |                 |                |                                  | 32P2W-A | Wask Row Version       |

| M37477M8-XXXSP |                 |                | Input ports: 8                   | 32P4B   | Maala DOM              |

| M37477M8-XXXFP |                 |                | (Including 4 analog              | 32P2W-A | Mask ROM version       |

| M37477M8TXXXSP |                 |                | input pins.)                     | 32P4B   | Mari DOM*              |

| M37477M8TXXXFP | 16384           | 384            |                                  | 32P2W-A | Mask ROM version*      |

| M37477E8-XXXSP | 10304           | 304            |                                  | 32P4B   | C T' DDOM '            |

| M37477E8-XXXFP |                 |                |                                  | 32P2W-A | One Time PROM version  |

| M37477E8TXXXSP |                 |                |                                  | 32P4B   |                        |

| M37477E8TXXXFP |                 |                |                                  | 32P2W-A | One Time PROM version* |

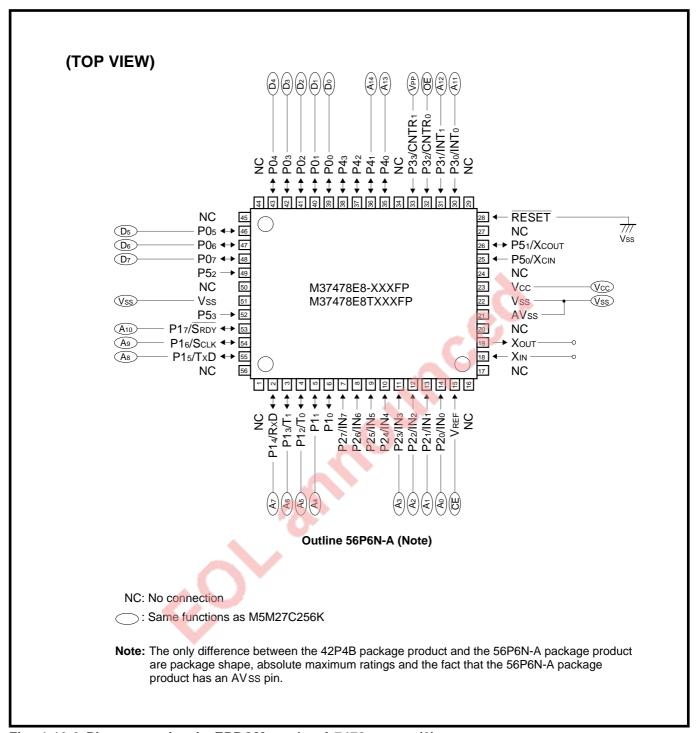

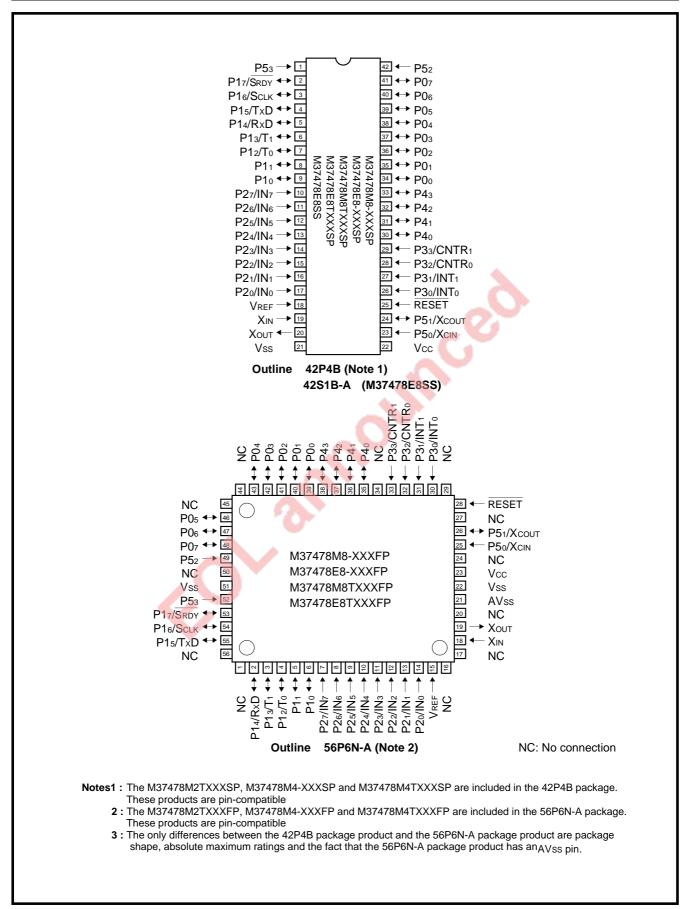

| M37478M2TXXXSP |                 |                |                                  | 42P4B   | *                      |

| M37478M2TXXXFP | 4096            | 128            |                                  | 56P6N-A | Mask ROM version*      |

| M37478M4-XXXSP |                 |                |                                  | 42P4B   |                        |

| M37478M4-XXXFP |                 |                |                                  | 56P6N-A | Mask ROM version       |

| M37478M4TXXXSP | 8192            | 192            |                                  | 42P4B   | *                      |

| M37478M4TXXXFP |                 |                | I/O ports: 20                    | 56P6N-A | Mask ROM version*      |

| M37478M8-XXXSP |                 |                | Input ports: 16                  | 42P4B   |                        |

| M37478M8-XXXFP |                 |                | (Including 8 analog              | 56P6N-A | Mask ROM version       |

| M37478M8TXXXSP |                 |                | input pins.)                     | 42P4B   | <u>.</u>               |

| M37478M8TXXXFP |                 |                | iliput pilis.)                   | 56P6N-A | Mask ROM version*      |

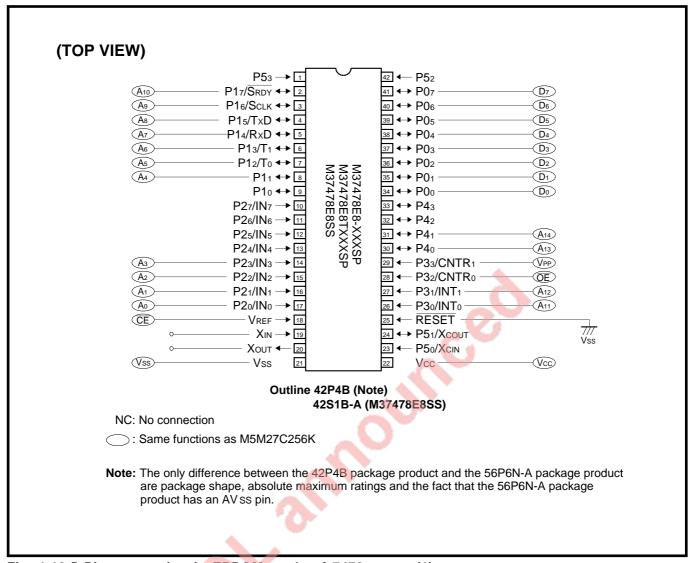

| M37478E8-XXXSP | 16384 384       | 384            |                                  | 42P4B   |                        |

|                |                 |                |                                  |         | One Time PROM version  |

| M37478E8-XXXFP |                 |                |                                  | 56P6N-A | _                      |

| M37478E8TXXXSP |                 |                |                                  | 42P4B   | One Time PROM version* |

| M37478E8TXXXFP |                 |                | 1/0                              | 56P6N-A |                        |

| M37478E8SS     | 16384           | 384            | I/O ports: 20<br>Input ports: 16 | 42S1B-A | EPROM version          |

| M37478RSS      | 63.5K<br>(Note) | 384            | (Including 8 analog input pins.) | 42S1M   | Emulator MCU           |

Note: Address space usable as a ROM area.

<sup>\* :</sup> Extended operating temperature version.

# 1.3 Performance overview

#### 1.3 Performance overview

Tables 1.3.1 to 1.3.4 show the performance overview of 7470/7471/7477/7478 group.

Table 1.3.1 Performance overview of 7470 group

|                                             |               | meter             | Functions                                                          |

|---------------------------------------------|---------------|-------------------|--------------------------------------------------------------------|

|                                             |               |                   | 71 (69 basic instructions of 740 family and 2 multiplication       |

| Number of basic instructions                |               |                   | and division instructions)                                         |

|                                             |               |                   | $0.5~\mu s$ (the minimum instructions, at 8 MHz clock input        |

| Instruction                                 | execution t   | ime               | oscillation frequency)                                             |

| Clock inpu                                  | t oscillation | frequency         | 8 MHz (max.)                                                       |

|                                             |               | M37470M2          | 4096 bytes                                                         |

|                                             | ROM           | M37470M4/E4       | 8192 bytes                                                         |

| Memory                                      |               | M37470M8/E8       | 16384 bytes                                                        |

| size                                        |               | M37470M2          | 128 bytes                                                          |

|                                             | RAM           | M37470M4/E4       | 192 bytes                                                          |

|                                             |               | M37470M8/E8       | 384 bytes                                                          |

|                                             |               | P0                | 8-bit                                                              |

| Input/                                      | I/O           | P1                | 8-bit                                                              |

| Output                                      | 1/0           | P2                | 4-bit                                                              |

| port                                        |               | P4                | 2-bit                                                              |

|                                             | Input         | P3                | 4-bit                                                              |

| Serial I/O                                  |               |                   | 8-bit X 1                                                          |

| Timers                                      |               |                   | 8-bit timer X 4                                                    |

| PWM                                         |               |                   | 1 (in common with 2 timer)                                         |

| A-D conve                                   | rter          |                   | 8-bit X 1 (4 channels)                                             |

|                                             |               | M37470M2          | 64 levels max.                                                     |

| Subroutine                                  | nesting       | M37470M4/E4       | 96 levels max.                                                     |

|                                             |               | M37470M8/E8       | 192 levels max.                                                    |

| Interrupt                                   |               |                   | 5 external interrupts, 6 internal interrupts, 1 software interrupt |

| Clock gene                                  | erating circu | it .              | Built-in circuit with internal feedback resistor (an external      |

| Olock gene                                  |               |                   | ceramic resonator or a quartz-crystal oscillator)                  |

|                                             |               |                   | 2.7 V to 4.5 V                                                     |

| Power sou                                   | rce voltage   | , <b>( )</b> '    | (at (2.2 Vcc-2) MHz clock input oscillation frequency)             |

| l ower sou                                  | ree voltage   |                   | 4.5 V to 5.5 V                                                     |

|                                             |               |                   | (at 8 MHz clock input oscillation frequency)                       |

| Power diss                                  | sination      |                   | 35 mW typ.                                                         |

|                                             | •             | †                 | (at 8 MHz clock input oscillation frequency)                       |

| Input/Output Input/Output withstand voltage |               |                   | 5 V                                                                |

| characteristics Output current              |               |                   | -5 mA to +10 mA (P0, P1, P2, P4: CMOS 3-state)                     |

|                                             | temperature   | 1                 | -20 °C to +85 °C                                                   |

| Device structure                            |               | <u> </u>          | CMOS silicon gate                                                  |

| Package M37470Mx/Ex-XXXSP                   |               | M37470Mx/Ex-XXXSP | 32-pin shrink plastic molded DIP                                   |

Table 1.3.2 Performance overview of 7471 group

| Parameter                                   |               | meter                          | Functions                                                                               |  |  |

|---------------------------------------------|---------------|--------------------------------|-----------------------------------------------------------------------------------------|--|--|

| Number of basic instructions                |               |                                | 71 (69 basic instructions of 740 family and 2 multiplication and division instructions) |  |  |

| Instruction execution time                  |               |                                | $0.5~\mu s$ (the minimum instructions, at 8 MHz clock input oscillation frequency)      |  |  |

| Clock inpu                                  | t oscillation | frequency                      | 8 MHz (max.)                                                                            |  |  |

| •                                           |               | M37471M2                       | 4096 bytes                                                                              |  |  |

|                                             | ROM           | M37471M4/E4                    | 8192 bytes                                                                              |  |  |

| Memory                                      | 110           | M37471M8/E8                    | 16384 bytes                                                                             |  |  |

| size                                        |               | M37471M2                       | 128 bytes                                                                               |  |  |

| 0.20                                        | RAM           | M37471M4/E4                    | 192 bytes                                                                               |  |  |

|                                             | TO W          | M37471M8/E8                    | 384 bytes                                                                               |  |  |

|                                             |               | P0                             | 8-bit                                                                                   |  |  |

|                                             |               | P1                             | 8-bit                                                                                   |  |  |

| Input/                                      | I/O           | P2                             | 8-bit                                                                                   |  |  |

| Output                                      |               | P4                             | 4-bit                                                                                   |  |  |

| port                                        |               | P3                             | 4-bit                                                                                   |  |  |

|                                             | Input         | P5                             | 4-bit                                                                                   |  |  |

| Serial I/O                                  |               | 1 0                            | 8-bit X 1                                                                               |  |  |

| Timers                                      |               |                                | 8-bit timer X 4                                                                         |  |  |

| PWM                                         |               |                                | 1 (in common with 2 timer)                                                              |  |  |

| A-D conve                                   | rter          |                                | 8-bit X 1 (8 channels)                                                                  |  |  |

| A D CONVC                                   | 1101          | M37471M2                       | 64 levels max.                                                                          |  |  |

| Subroutine                                  | nestina       | M37471M2/E4                    | 96 levels max.                                                                          |  |  |

| Cabicatine                                  | , nesting     | M37471M4/E4<br>M37471M8/E8     | 192 levels max.                                                                         |  |  |

| Interrupt                                   |               | WOT 47 TWO/LO                  | 5 external interrupts, 6 internal interrupts, 1 software interrupt                      |  |  |

| •                                           |               | _                              | Built-in circuit with internal feedback resistor (an external                           |  |  |

| Clock gene                                  | erating circu | it                             | ceramic resonator or a quartz-crystal oscillator)                                       |  |  |

|                                             |               | <del></del>                    | Built-in circuit with internal feedback resistor (a guartz-                             |  |  |

| Sub-clock                                   | generating of | circuit                        | crystal oscillator)                                                                     |  |  |

|                                             |               |                                | 2.7 V to 4.5 V                                                                          |  |  |

|                                             |               |                                | (at (2.2 Vcc-2) MHz clock input oscillation frequency)                                  |  |  |

| Power sou                                   | rce voltage   |                                | 4.5 V to 5.5 V                                                                          |  |  |

|                                             |               |                                | (at 8 MHz clock input oscillation frequency)                                            |  |  |

|                                             |               |                                | 35 mW typ.                                                                              |  |  |

| Power diss                                  | sipation      |                                | (at 8 MHz clock input oscillation frequency)                                            |  |  |

| Input/Output Input/Output withstand voltage |               | Input/Output withstand voltage | 5 V                                                                                     |  |  |

| characteristics Output current              |               |                                | -5 mA to +10 mA (P0, P1, P2, P4: CMOS 3-state)                                          |  |  |

| Operating temperature                       |               |                                | -20 °C to +85 °C                                                                        |  |  |

| Device structure                            |               |                                | CMOS silicon gate                                                                       |  |  |

| 250 511                                     |               | M37471Mx/Ex-XXXSP              | 42-pin shrink plastic molded DIP                                                        |  |  |

| Package                                     |               | M37471Mx/Ex-XXXFP              | 56-pin plastic molded QFP                                                               |  |  |

|                                             |               | M37471E8SS                     | 42-pin shrink ceramic DIP                                                               |  |  |

|                                             |               | IVIOTAT ILUGO                  | 72 pm ominik ocianno Dn                                                                 |  |  |

# 1.3 Performance overview

Table 1.3.3 Performance overview of 7477 group

|                                                    | Parai         | meter             | Functions                                                                      |  |

|----------------------------------------------------|---------------|-------------------|--------------------------------------------------------------------------------|--|

| Number of basic instructions                       |               |                   | 71 (69 basic instructions of 740 family and 2 multiplication                   |  |

| Number of basic instructions                       |               |                   | and division instructions)                                                     |  |

| In other sations                                   | avanution t   | ·                 | 0.5 $\mu$ s (the minimum instructions, at 8 MHz clock input                    |  |

| Instruction                                        | execution t   | ime               | oscillation frequency)                                                         |  |

| Clock inpu                                         | t oscillation | frequency         | 8 MHz (max.)                                                                   |  |

|                                                    |               | M37477M2          | 4096 bytes                                                                     |  |

|                                                    | ROM           | M37477M4          | 8192 bytes                                                                     |  |

| Memory                                             |               | M37477M8/E8       | 16384 bytes                                                                    |  |

| size                                               |               | M37477M2          | 128 bytes                                                                      |  |

|                                                    | RAM           | M37477M4          | 192 bytes                                                                      |  |

|                                                    |               | M37477M8/E8       | 384 bytes                                                                      |  |

|                                                    |               | P0                | 8-bit                                                                          |  |

| Input/                                             | I/O           | P1                | 8-bit                                                                          |  |

| Output                                             |               | P4                | 2-bit                                                                          |  |

| port                                               | Input         | P2                | 4-bit                                                                          |  |

|                                                    | Impat         | P3                | 4-bit                                                                          |  |

| Serial I/O                                         |               |                   | 8-bit X 1 (operable in UART mode)                                              |  |

| Timers                                             |               |                   | 8-bit timer X 4                                                                |  |

| PWM                                                |               |                   | 1 (in common with 2 timer)                                                     |  |

| A-D conve                                          | rter          |                   | 8-bit X 1 (4 channels)                                                         |  |

|                                                    |               | M37477M2          | 64 level max.                                                                  |  |

| Subroutine                                         | nesting       | M37477M4          | 96 level max.                                                                  |  |

|                                                    |               | M37477M8/E8       | 192 level max.                                                                 |  |

| Interrupt                                          |               |                   | 5 external interrupts, 7 internal interrupts, 1 software interrupt             |  |

| Clock gene                                         | erating circu | i <del>t</del>    | Built-in circuit with internal feedback resistor (an external                  |  |

| Clock gene                                         | erating circu | II.               | ceramic resonator or a quartz-crystal oscillator)                              |  |

|                                                    |               |                   | 2.7 V to 4.5 V                                                                 |  |

| Power sou                                          | rce voltage   | 10                | (at (2.2 Vcc-2) MHz clock input oscillation frequency)                         |  |

| 1 OWEL 300                                         | ree voltage   |                   | 4.5 V to 5.5 V                                                                 |  |

|                                                    |               |                   | (at 8 MHz clock input oscillation frequency)                                   |  |

| Power diss                                         | sination      |                   | 35 mW typ.                                                                     |  |

|                                                    | <u> </u>      |                   | (at 8 MHz clock input oscillation frequency)                                   |  |

| Input/Output <u>Input/Output withstand voltage</u> |               |                   | 5 V                                                                            |  |

|                                                    |               | Output current    | -5 mA to +10 mA (P0, P1, P4: CMOS 3-state)                                     |  |

| Operating temperature                              |               |                   | -20 °C to +85 °C (-40 °C to +85 °C for extended operating temperature version) |  |

| Device structure                                   |               |                   | CMOS silicon gate                                                              |  |

|                                                    |               | M37477Mx/E8-XXXSP | 32-pin shrink plastic molded DIP                                               |  |

| Package                                            |               | M37477Mx/E8TXXXSP | - F S President merede and                                                     |  |

| rackage                                            |               | M37477Mx/E8-XXXFP | 32-pin plastic molded SOP                                                      |  |

|                                                    |               | M37477Mx/E8TXXXFP | or him bracing information of                                                  |  |

Table 1.3.4 Performance overview of 7478 group

|                              | Parai          | meter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Functions                                                                      |

|------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71 (69 basic instructions of 740 family and 2 multiplication                   |

| Number of basic instructions |                | uctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | and division instructions)                                                     |

|                              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.5 $\mu$ s (the minimum instructions, at 8 MHz clock input                    |

| Instruction                  | execution ti   | ime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | oscillation frequency)                                                         |

| Clock input                  | t oscillation  | frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 MHz (max.)                                                                   |

| Olock Input                  | Oscillation    | M37478M2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4096 bytes                                                                     |

|                              | ROM            | M37478M4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8192 bytes                                                                     |

| Memory                       | KOW            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16384 bytes                                                                    |

| size                         |                | M37478M8/E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                              |

| 3126                         | D 4 4 4        | M37478M2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 128 bytes                                                                      |

|                              | RAM            | M37478M4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 192 bytes                                                                      |

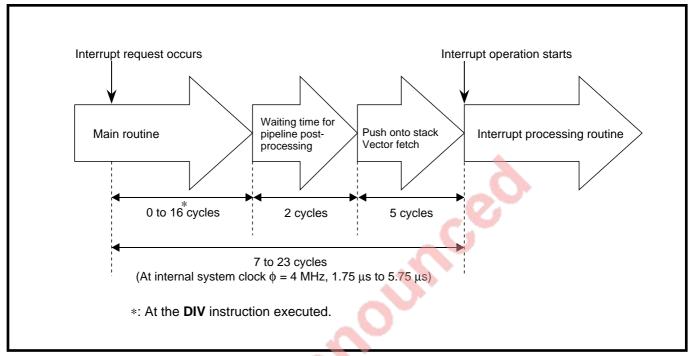

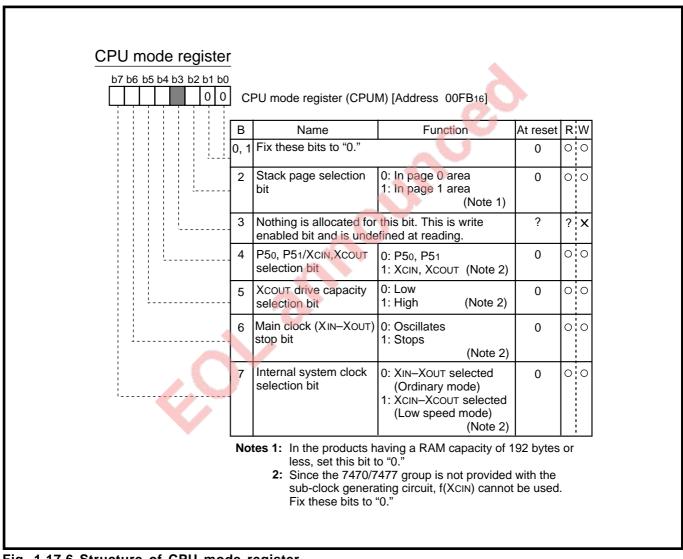

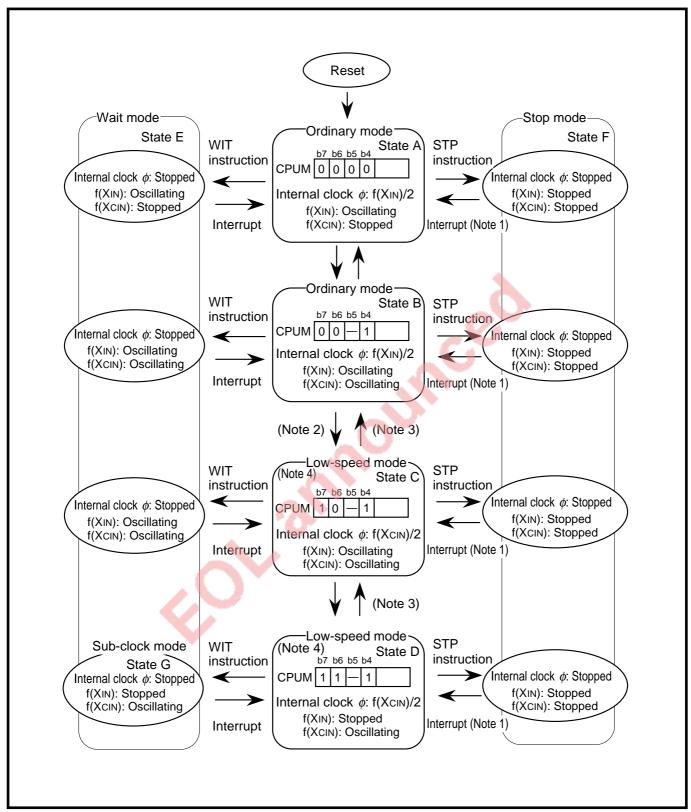

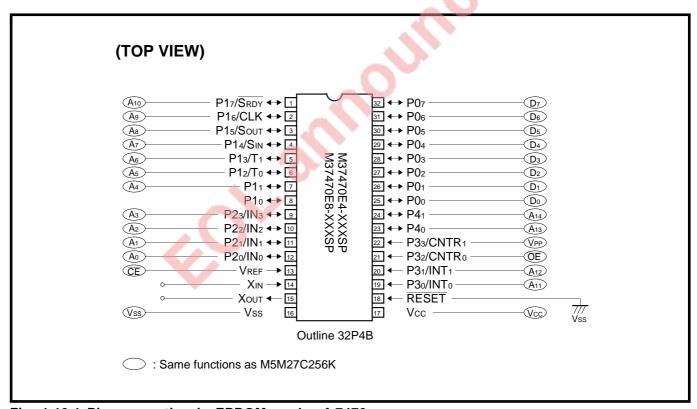

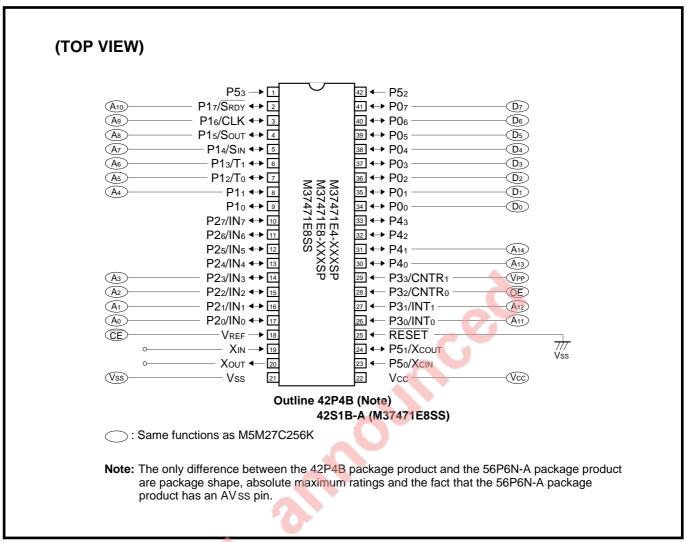

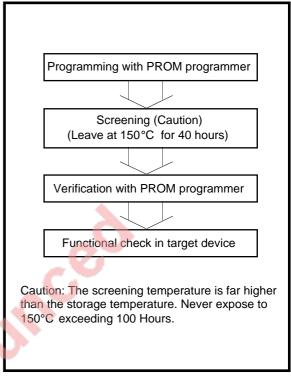

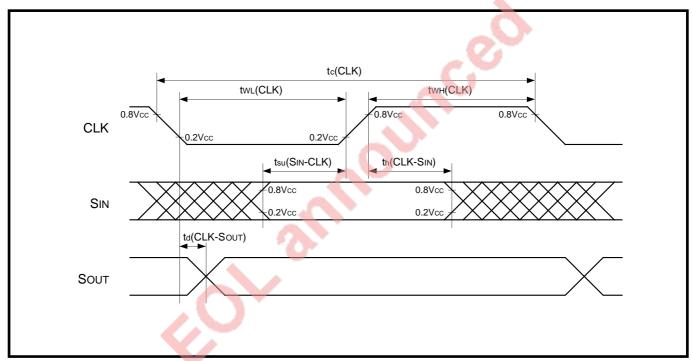

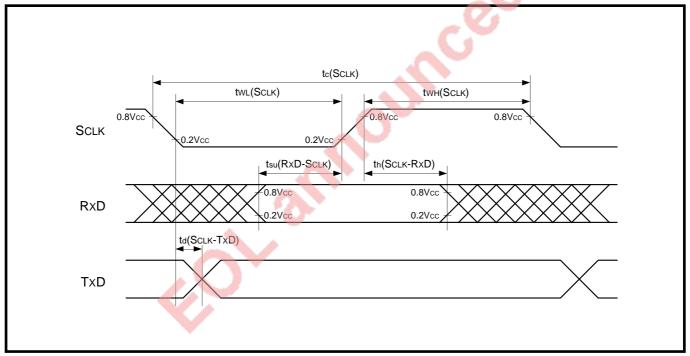

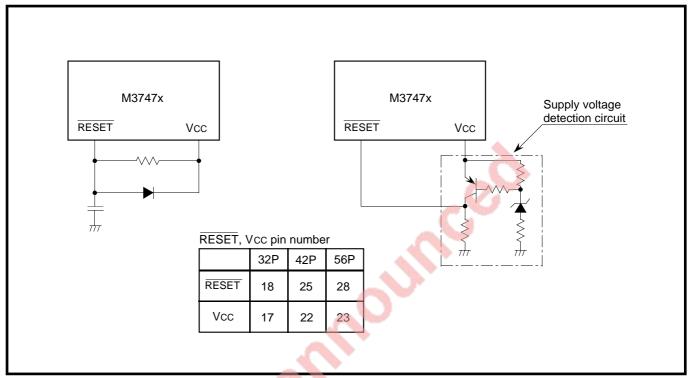

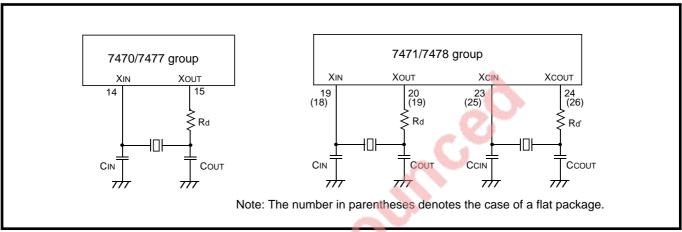

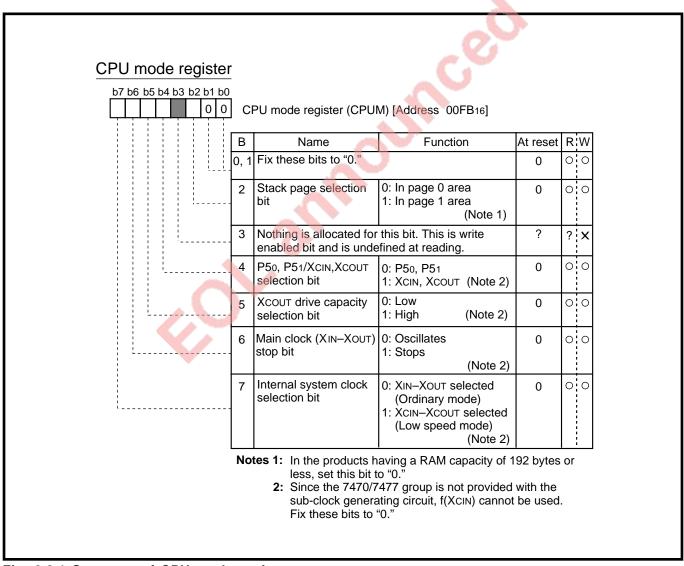

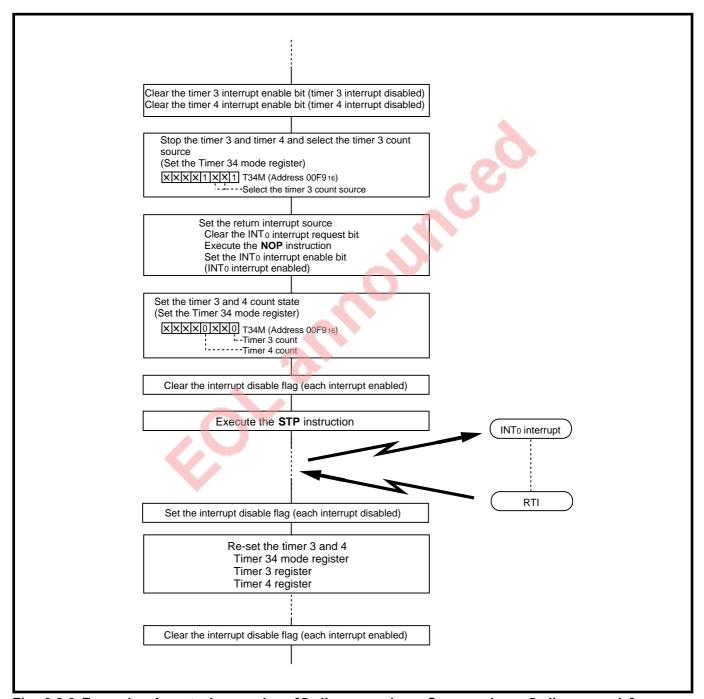

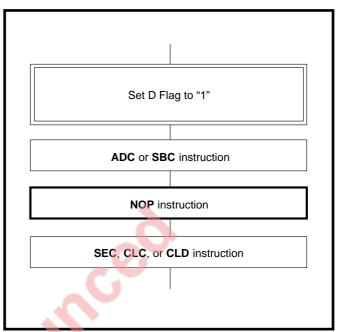

|                              |                | M37478M8/E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 384 bytes                                                                      |