## PLC42VA12

24 VCC

#### DESCRIPTION

The new PLC42VA12 CMOS PLD from Philips Semiconductors exhibits a unique combination of the two architectural concepts that revolutionized the PLD marketplace.

The Philips Semiconductors unique Output Macro Cell (OMC) embodies all the advantages and none of the disadvantages associated with the "V" type Output Macro Cell devices. This new design, combined with added functionality of two programmable arrays, represents a significant advancement in the configurability and efficiency of multi-function PLDs.

The most significant improvement in the Output Macro Cell structure is the implementation of the register bypass function. Any of the 10 J-K/D registers can be individually bypassed, thus creating a combinatorial I/O path from the AND array to the output pin. Unlike other "V" type devices, the register in the PLC42VA12 Macro Cell remains fully functional as a buried register. Both the combinatorial I/O and buried register have separate input paths (from the AND array). In most V-type architectures, the register is lost as a resource when the cell is configured as a combinatorial I/O. This feature provides the capability to operate the buried register independently from the combinatorial I/O.

The PLC42VA12 is an EPROM-based CMOS device. Designs can be generated using Philips Semiconductors SNAP PLD design software packages or one of several other commercially available JEDEC standard PLD design software packages.

## FEATURES

- High-speed EPROM-based CMOS Multi-Function PLD

- Super set of 22V10, 32VX10 and 20RA10 PAL® ICs

- Two fully programmable arrays eliminate "P-term Depletion"

- Up to 64 P-terms per OR function

- Improved Output Macro Cell Structure

- Individually programmable as:

- \* Registered Output with feedback

- \* Registered Input

- \* Combinatorial I/O with Buried Register

- \* Dedicated I/O with feedback

- \* Dedicated Input (combinatorial)

- Bypassed Registers are 100% functional with separate input and feedback paths

- Individual Output Enable control functions

- \* From pin or AND array

- Reprogrammable 100% tested for programmability

- Eleven clock sources

- Register Preload and Diagnostic Test Mode Features

- Security fuse

## **APPLICATIONS**

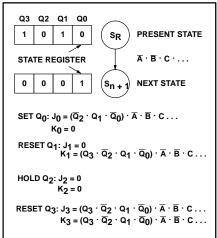

- Mealy or Moore State Machines

- Synchronous

- Asynchronous

- Multiple, independent State Machines

- 10-bit ripple cascade

- Sequence recognition

- Bus Protocol generation

- Industrial control

- A/D Scanning

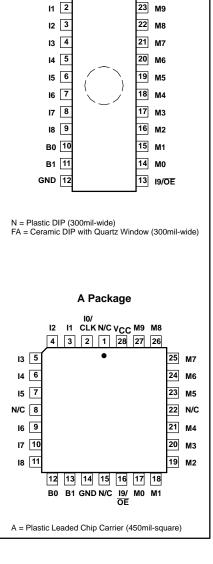

10/CLK 1

FA and N Pack-

ages

#### ORDERING INFORMATION

| DESCRIPTION                                                                | ORDER CODE  | DRAWING NUMBER |

|----------------------------------------------------------------------------|-------------|----------------|

| 24-Pin Ceramic Dual In-Line with window,<br>Reprogrammable (300mil-wide)   | PLC42VA12FA | 1478A          |

| 24-Pin Plastic Dual In-Line,<br>One Time Programmable (300mil-wide)        | PLC42VA12N  | 0410D          |

| 28-Pin Plastic Leaded Chip Carrier,<br>One Time Programmable (450mil-wide) | PLC42VA12A  | 0401F          |

PAL is a registered trademark of Advanced Micro Devices, Inc.

## PLC42VA12

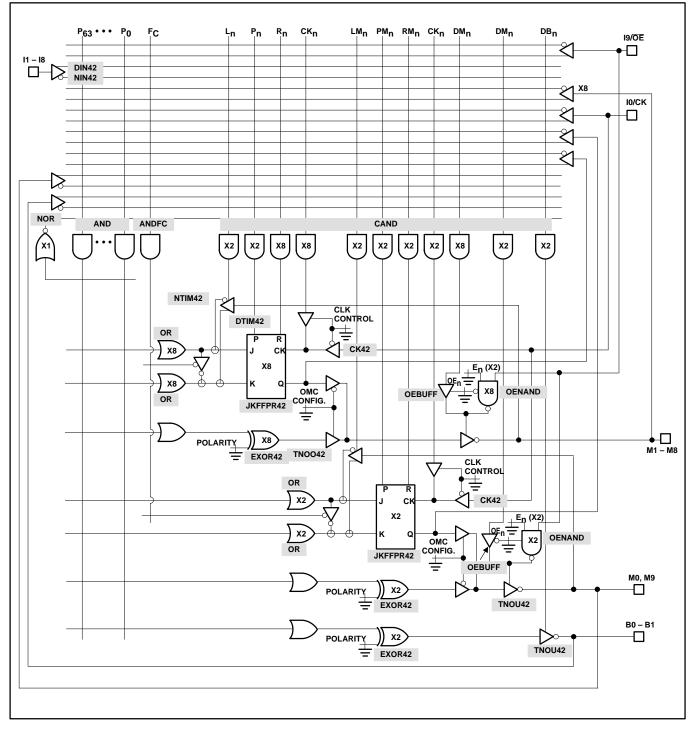

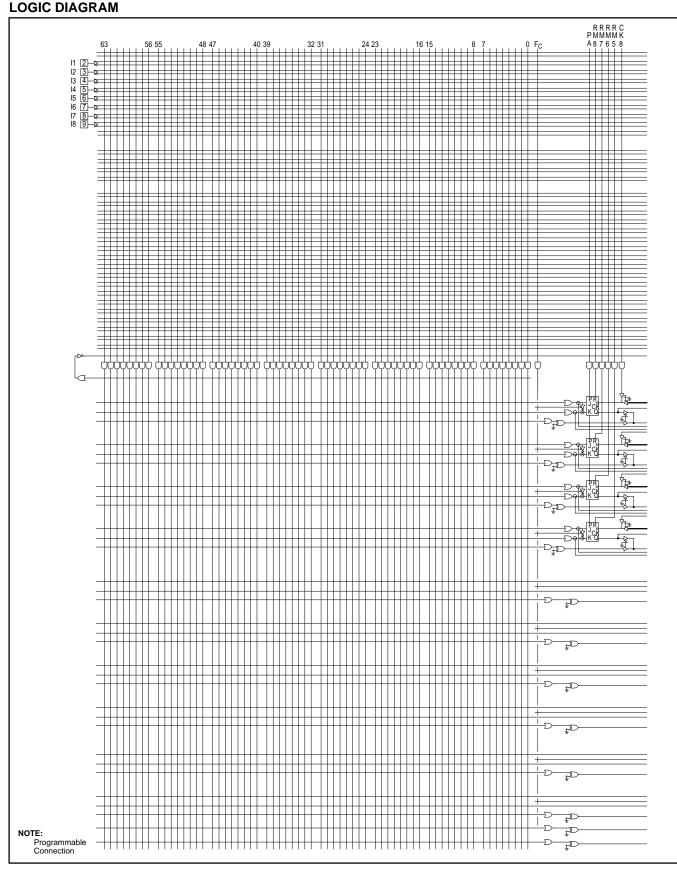

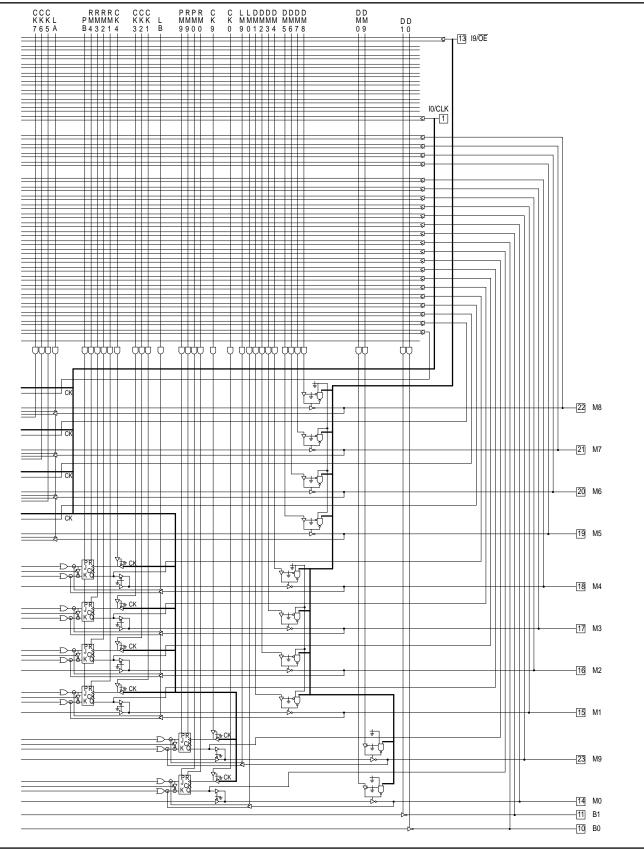

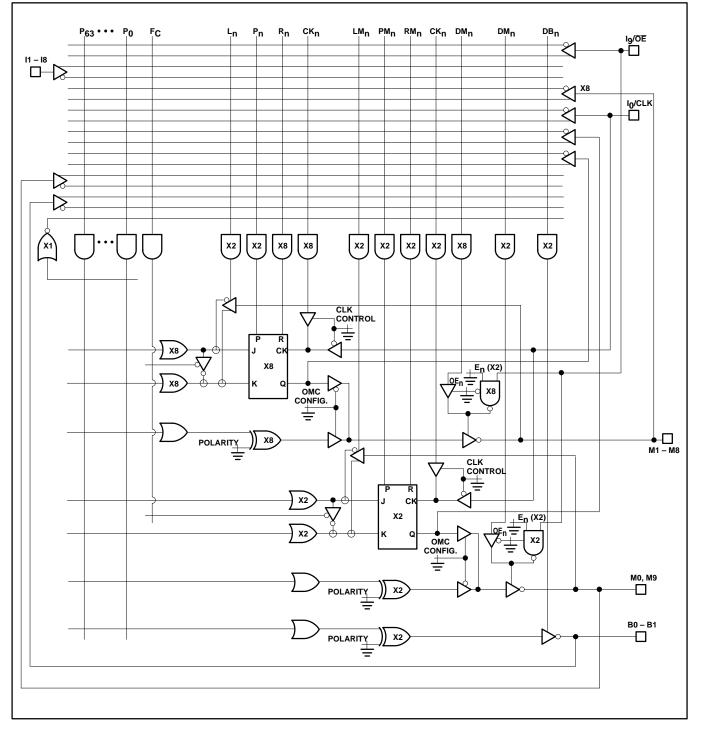

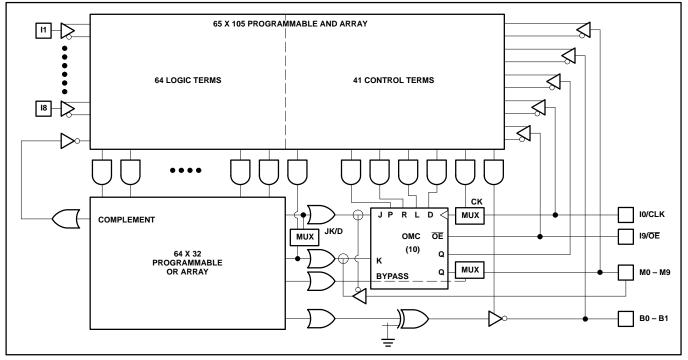

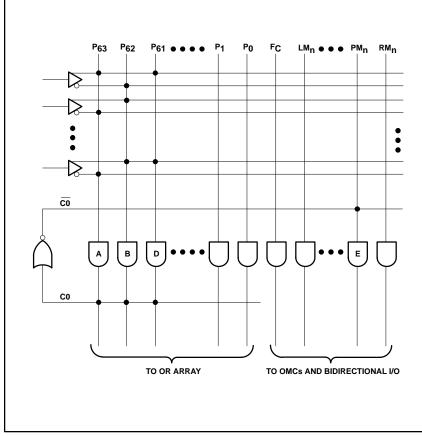

## LOGIC DIAGRAM

PLC42VA12

#### LOGIC DIAGRAM (Continued)

## PLC42VA12

## **FUNCTIONAL DIAGRAM**

## PLC42VA12

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL           | PARAMETER                   | RATINGS                      | UNIT            |

|------------------|-----------------------------|------------------------------|-----------------|

| V <sub>CC</sub>  | Supply voltage              | –0.5 to +7                   | V <sub>DC</sub> |

| V <sub>IN</sub>  | Input voltage               | –0.5 to V <sub>CC</sub> +0.5 | V <sub>DC</sub> |

| V <sub>OUT</sub> | Output voltage              | –0.5 to V <sub>CC</sub> +0.5 | V <sub>DC</sub> |

| I <sub>IN</sub>  | Input currents              | -10 to +10                   | mA              |

| I <sub>OUT</sub> | Output currents             | +24                          | mA              |

| T <sub>amb</sub> | Operating temperature range | 0 to +75                     | °C              |

| T <sub>stg</sub> | Storage temperature range   | -65 to +150                  | °C              |

#### THERMAL RATINGS

| TEMPERATURE                                      |       |

|--------------------------------------------------|-------|

| Maximum junction                                 | 150°C |

| Maximum ambient                                  | 75°C  |

| Allowable thermal<br>rise ambient to<br>junction | 75°C  |

#### NOTE:

1. Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

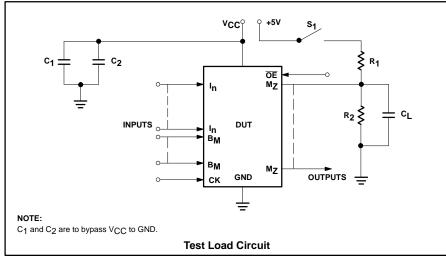

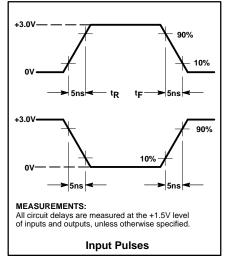

## AC TEST CONDITIONS

## **VOLTAGE WAVEFORMS**

## PLC42VA12

## DC ELECTRICAL CHARACTERISTICS

$0^{\circ}C \le T_{amb} \le +75^{\circ}C, 4.75V \le V_{CC} \le 5.25V$

|                     |                                                      |                                                                      |      | LIMITS           |                       |          |  |

|---------------------|------------------------------------------------------|----------------------------------------------------------------------|------|------------------|-----------------------|----------|--|

| SYMBOL PARAMETER    |                                                      | TEST CONDITION                                                       | MIN  | TYP <sup>1</sup> | MAX                   | UNIT     |  |

| Input volt          | age <sup>2</sup>                                     | •                                                                    |      |                  |                       |          |  |

| V <sub>IL</sub>     | Low                                                  | V <sub>CC</sub> = MIN                                                | -0.3 |                  | 0.8                   | V        |  |

| V <sub>IH</sub>     | High                                                 | V <sub>CC</sub> = MAX                                                | 2.0  |                  | V <sub>CC</sub> + 0.3 | V        |  |

| Output vo           | ltage <sup>2</sup>                                   | · · · ·                                                              |      |                  |                       |          |  |

| V <sub>OL</sub>     | Low                                                  | $V_{CC} = MIN; I_{OL} = 16mA$                                        |      | 0.3              | 0.5                   | V        |  |

| V <sub>OH</sub>     | High                                                 | $V_{CC} = MIN; I_{OH} = -3.2mA$ 2.4                                  |      | 4.3              |                       | V        |  |

| Input curr          | ent                                                  |                                                                      |      |                  |                       |          |  |

| IIL                 | Low                                                  | V <sub>IN</sub> = GND                                                |      | -1               | -10                   | μA       |  |

| I <sub>IH</sub>     | High                                                 | $V_{IN} = V_{CC}$                                                    |      | +1               | 10                    | μA       |  |

| Output cu           | rrent                                                |                                                                      |      |                  | -                     |          |  |

| I <sub>O(OFF)</sub> | Hi-Z state                                           | Z state V <sub>OUT</sub> = V <sub>CC</sub><br>V <sub>OUT</sub> = GND |      | 1<br>_1          | 10<br>-10             | μΑ<br>μΑ |  |

| I <sub>OS</sub>     | Short-circuit <sup>3,7</sup>                         | V <sub>OUT</sub> = GND                                               |      |                  | -130                  | mA       |  |

| I <sub>CC1</sub>    | V <sub>CC</sub> supply current (Active) <sup>4</sup> | $I_{OUT} = 0$ mA, f = 15MHz <sup>6</sup> , V <sub>CC</sub> = MAX     |      | 90               | 120                   | mA       |  |

| I <sub>CC2</sub>    | V <sub>CC</sub> supply current (Active) <sup>5</sup> | $I_{OUT} = 0$ mA, f = 15MHz <sup>6</sup> , V <sub>CC</sub> = MAX     |      | 70               | 100                   | mA       |  |

| Capacitar           | ce                                                   | •                                                                    |      | -                |                       |          |  |

| CI                  | Input                                                | $V_{CC} = 5V; V_{IN} = 2.0V$                                         |      | 12               |                       | pF       |  |

| CB                  | I/O                                                  | V <sub>B</sub> = 2.0V                                                |      | 15               |                       | pF       |  |

NOTES:

1. All typical values are at  $V_{CC} = 5V$ .  $T_{amb} = +25^{\circ}C$ .

2. All voltage values are with respect to network ground terminal.

3. Duration of short-circuit should not exceed one second. Test one at a time.

4. Tested with V<sub>IL</sub> = 0.45V, V<sub>IH</sub> = 2.4V.

5. Tested with  $V_{IL} = 0V$ ,  $V_{IH} = V_{CC}$ .

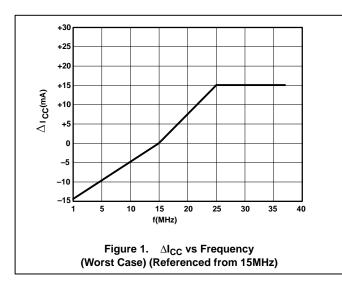

Refer to Figure 1,  $\Delta I_{CC}$  vs Frequency (worst case). (Referenced from 15MHz) The I<sub>CC</sub> increases by 1.5mA per MHz for the frequency range of 16MHz up to 25MHz. 6. The I<sub>CC</sub> remains at a worst case for the frequency range of 26MHz up to 37MHz. The I<sub>CC</sub> decreases by 1.0mA per MHz for the frequency range of 14MHz down to 1MHz.

The worst case I<sub>CC</sub> is calculated as follows:

- All dedicated inputs are switching.

All OMCs are configured as JK flip-flops in the toggle mode. . .all are toggling.

\_ All 12 outputs are disabled.

The number of product terms connected does not impact the I<sub>CC</sub>.

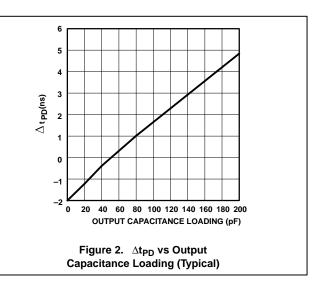

7. Refer to Figure 2 for  $\Delta t_{PD}$  vs output capacitance loading.

## PLC42VA12

## AC ELECTRICAL CHARACTERISTICS

$0^{\circ}C \leq T_{amb} \leq$  +75°C, 4.75V  $\leq$  V\_{CC}  $\leq$  5.25V; R\_1 = 238\Omega, R\_2 = 170 $\Omega$

|                               |                                                                                                                             |                   |                       | TEST <sup>2</sup>                  | PLC42VA12 |                  |     |      |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|------------------------------------|-----------|------------------|-----|------|

| SYMBOL                        | PARAMETER                                                                                                                   | FROM              | то                    | CONDITION<br>(C <sub>L</sub> (pF)) | MIN       | TYP <sup>1</sup> | МАХ | UNIT |

| Set-up Ti                     | ne                                                                                                                          | •                 |                       |                                    |           |                  |     |      |

| t <sub>IS1</sub>              | Input; dedicated clock                                                                                                      | (I, B, M) +/-     | CK+                   | 50                                 | 23        | 16               |     | ns   |

| t <sub>IS2</sub>              | Input; P-term clock                                                                                                         | (I, B, M) +/-     | (I, B, M) +/-         | 50                                 | 20        | 13               |     | ns   |

| t <sub>IS3</sub> 3            | Preload; dedicated clock                                                                                                    | (M) +/-           | CK+                   | 50                                 | 10        | 3.5              |     | ns   |

| t <sub>IS4</sub> 3            | Preload; P-term clock                                                                                                       | (M) +/-           | (I, B, M) +/-         | 50                                 | 2         | -1.0             |     | ns   |

| t <sub>IS5</sub> 3            | Input through complement array;<br>dedicated clock                                                                          | (I, B, M) +/-     | CK+                   | 50                                 | 50        | 34               |     | ns   |

| t <sub>IS6</sub> 3            |                                                                                                                             |                   | (I, B, M) +/-         | 50                                 | 40        | 30               |     | ns   |

| Propagat                      | on Delay                                                                                                                    | -                 | -                     | -                                  | -         | -                |     | _    |

| t <sub>PD1</sub>              | Propagation Delay                                                                                                           | (I, B, M) +/-     | (I, B, M) +/-         | 50                                 |           | 20               | 35  | ns   |

| t <sub>PD2</sub>              | Propagation Delay with complement array (2 passes)                                                                          | (I, B,) +/–       | (I, B, M) +/-         | 50                                 |           | 36               | 55  | ns   |

| t <sub>CKO1</sub>             | Clock to Output; Dedicated clock                                                                                            | CK+               | (M) +/-               | 50                                 |           | 13               | 17  | ns   |

| t <sub>CKO2</sub>             | Clock to output; P-term clock                                                                                               | (I, B, M) +/-     | (M) +/–               | 50                                 |           | 18               | 27  | ns   |

| t <sub>RP1</sub>              | Registered operating period;<br>Dedicated clock ( $t_{IS1} + t_{CKO1}$ )                                                    | (I, B, M) +/-     | (M) +/-               | 50                                 |           | 29               | 40  | ns   |

| t <sub>RP2</sub>              | Registered operating period;<br>P-term clock (t <sub>IS2</sub> + t <sub>CKO2</sub> )                                        | (I, B, M) +/-     | (M) +/-               | 50                                 |           | 31               | 47  | ns   |

| t <sub>RP3</sub> 3            | Register preload operating period;<br>Dedicated clock (t <sub>IS3</sub> + t <sub>CKO1</sub> )                               | (M) +/-           | (M) +/-               | 50                                 |           | 16.5             | 27  | ns   |

| t <sub>RP4</sub> 3            | Register preload operating period;<br>P-term clock (t <sub>IS4</sub> + t <sub>CKO2</sub> )                                  | (M) +/-           | (M) +/-               | 50                                 |           | 17               | 29  | ns   |

| t <sub>RP5</sub> 3            | Registered operating period with comple-<br>ment array; dedicated clock (t <sub>IS5</sub> + (I, B, M<br>t <sub>CKO1</sub> ) |                   | (M) +/–               | 50                                 |           | 47               | 67  | ns   |

| t <sub>RP6</sub> 3            | Registered operating period with<br>complement array; P-term clock<br>(t <sub>IS6</sub> + t <sub>CKO2</sub> )               | (I, B, M) +/-     | (M) +/                | 50                                 |           | 48               | 67  | ns   |

| t <sub>OE1</sub>              | Output Enable; from /OE pin <sup>4</sup>                                                                                    | /OE –             | (M) +/-               | 50                                 |           | 10               | 20  | ns   |

| t <sub>OE2</sub>              | Output Enable; from P-term <sup>4</sup>                                                                                     | (I, B, M) +/-     | (B, M) +/-            | 50                                 |           | 12.5             | 25  | ns   |

| t <sub>OD1</sub>              | Output Disable; from /OE pin <sup>4</sup>                                                                                   | /OE +             | Outputs dis-<br>abled | 5                                  |           | 10               | 20  | ns   |

| t <sub>OD2</sub>              | Output Disable; from P-term <sup>4</sup>                                                                                    | (I, B, M) +/-     | Outputs dis-<br>abled | 5                                  |           | 14.5             | 25  | ns   |

| t <sub>PRO</sub> 3            | Preset to Output                                                                                                            | (I, B, M) +/-     | (M) +/-               | 50                                 |           | 25               | 35  | ns   |

| t <sub>PPR</sub> <sup>3</sup> | Power-on Reset (Mn = 1)                                                                                                     | V <sub>CC</sub> + | (M) +/-               | 50                                 |           |                  | 15  | ns   |

| Hold Time                     |                                                                                                                             |                   |                       |                                    |           |                  |     |      |

| t <sub>IH1</sub>              | Input (Dedicated clock)                                                                                                     | CK+               | (I, B, M) +/-         | 50                                 | 0         | -13              |     | ns   |

| t <sub>IH2</sub>              | Input (P-term clock)                                                                                                        | (I, B, M) +/-     | (I, B, M) +/-         | 50                                 | 5         | -7.5             |     | ns   |

| t <sub>IH3</sub> 3            | Input; from Mn (Dedicated clock)                                                                                            | CK+               | (M) +/–               | 50                                 | 5         | -1.5             |     | ns   |

| t <sub>IH4</sub> 3            | Input; from Mn (P-term clock)                                                                                               | (I, B, M) +/-     | (M) +/-               | 50                                 | 10        | 3.5              |     | ns   |

| Pulse Wid                     | lth                                                                                                                         |                   |                       |                                    |           |                  |     |      |

| t <sub>CKH1</sub>             | Clock High; Dedicated clock                                                                                                 | CK+               | CK–                   | 50                                 | 10        | 5                |     | ns   |

| t <sub>CKL1</sub>             | Clock Low; Dedicated clock                                                                                                  | CK–               | CK+                   | 50                                 | 10        | 5                |     | ns   |

| t <sub>CKH2</sub>             | Clock High; P-term clock                                                                                                    | CK+               | CK–                   | 50                                 | 15        | 7                |     | ns   |

| t <sub>CKL2</sub>             | Clock Low; P-term clock                                                                                                     | CK–               | CK+                   | 50                                 | 15        | 7                |     | ns   |

| t <sub>PRH</sub> <sup>3</sup> | Width of preset/reset input pulse                                                                                           | (I, B, M) +/-     | (I, B, M) +/-         | 50                                 | 30        | 7                |     | ns   |

## PLC42VA12

## AC ELECTRICAL CHARACTERISTICS (Continued)

|                                |                                                                                                                     |               |         | TEST <sup>2</sup>                  | PLC42VA12 |                  |     |      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------|---------|------------------------------------|-----------|------------------|-----|------|

| SYMBOL                         | PARAMETER                                                                                                           | FROM          | то      | CONDITION<br>(C <sub>L</sub> (pF)) | MIN       | TYP <sup>1</sup> | МАХ | UNIT |

| Frequenc                       | y of Operation                                                                                                      |               |         |                                    |           |                  |     |      |

| f <sub>CK1</sub>               | Dedicated clock frequency                                                                                           | C+            | C+      | 50                                 | 50        | 100              |     | MHz  |

| f <sub>CK2</sub>               | P-term clock frequency                                                                                              | C+            | C+      | 50                                 | 33        | 71.4             |     | MHz  |

| f <sub>MAX1</sub>              | Registered operating frequency;<br>Dedicated clock (t <sub>IS1</sub> + t <sub>CKO1</sub> )                          | (I, B, M) +/- | (M) +/– | 50                                 | 25        | 34.5             |     | MHz  |

| f <sub>MAX2</sub>              | Registered operating frequency;<br>P-term clock (t <sub>IS2</sub> + t <sub>CKO2</sub> )                             | (I, B, M) +/- | (M) +/- | 50                                 | 21.3      | 32.3             |     | MHz  |

| f <sub>MAX3</sub> 3            | Register preload operating frequency; Dedicated clock $(t_{IS3} + t_{CKO1})$                                        | (M) +/-       | (M) +/– | 50                                 | 37        | 60.6             |     | MHz  |

| f <sub>MAX4</sub> 3            | Register preload operating frequency; P-term clock (t <sub>IS4</sub> + t <sub>CKO2</sub> )                          | (M) +/-       | (M) +/- | 50                                 | 34.5      | 58.8             |     | MHz  |

| f <sub>MAX5</sub> <sup>3</sup> | Registered operating frequency<br>with complement array;<br>Dedicated clock (t <sub>IS5</sub> + t <sub>CKO1</sub> ) | (I, B, M) +/- | (M) +/- | 50                                 | 14.9      | 21.3             |     | MHz  |

| f <sub>MAX6</sub> <sup>3</sup> | Registered operating frequency<br>with complement array;<br>P-term clock ( $t_{IS6} + t_{CKO2}$ )                   | (I, B, M) +/- | (M) +/– | 50                                 | 14.9      | 20.8             |     | MHz  |

NOTES:

1. All typical values are at  $V_{CC} = 5V$ ,  $T_{amb} = +25^{\circ}C$ . These limits are not tested/guaranteed. 2. Refer also to AC Test Conditions (Test Load Circuit).

3. These limits are not tested, but are characterized periodically and are guaranteed by design.

4. For 3-State output; output enable times are tested with C<sub>L</sub> = 50pF to the 1.5V level, and S<sub>1</sub> is open for high-impedance to High tests and closed for high-impedance to Low tests. Output disable times are tested with C<sub>L</sub> = 5pF. High-to-High impedance tests are made to an output voltage of  $V_T = (V_{OL} - 0.5V)$  with S<sub>1</sub> open, and Low-to-High impedance tests are made to the  $V_T = (V_{OL} + 0.5V)$  level with S<sub>1</sub> closed.

## **BLOCK DIAGRAM**

## PLC42VA12

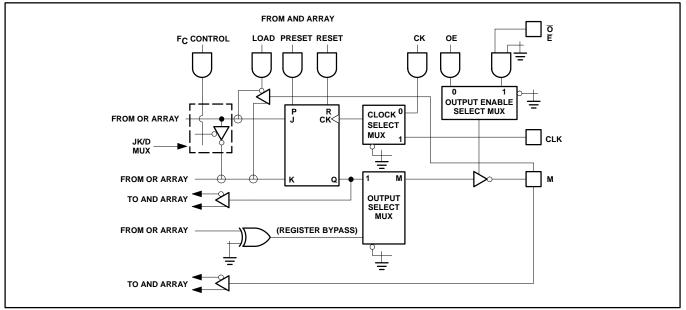

## **OUTPUT MACRO CELL (OMC)**

### **Output Macro Cell Configuration**

Philips Semiconductors unique Output Macro Cell design represents a significant advancement in the configurability of multi-function Programmable Logic Devices.

The PLC42VA12 has 10 programmable Output Macro Cells. Each can be individually programmed in any of 5 basic configurations:

- Dedicated I/O (combinatorial) with feedback to AND array

- Dedicated Input

- Combinatorial I/O with feedback and Buried Register with feedback (register bypass)

- Registered Input

- Registered Output with feedback

Each of the registered options can be further customized as J-K type or D-type, with either an internally derived clock (from the AND array) or clocked from an external source. With these additional programmable options, it is possible to program each Output Macro Cell in any one of 14 different configurations. These 14 configurations, combined with the fully programmable OR array, make the PLC42VA12 the most versatile and silicon efficient of all the Output Macro Cell-type PLDs.

The most significant Output Macro Cell (OMC) feature is the implementation of the register bypass function. Any of the 10 J-K/D registers can be individually bypassed, thus creating a combinatorial I/O path from the AND array to the output pin. Unlike other Output Macro Cell-type devices, the register in the OMC is fully functional as a buried register. Furthermore, both the combinatorial I/O and the buried register have separate input paths (from the AND array) and separate feedback paths (to the AND array). This feature provides the capability to operate the buried register independently from the combinatorial I/O.

The PLC42VA12 is ideally suited for both synchronous and asynchronous logic functions. Eleven clock sources – 10 driven from the AND array and one from an external source – make it possible to design synchronous state machine functions, event-driven state machine functions and combinatorial (asynchronous) functions all on the same chip.

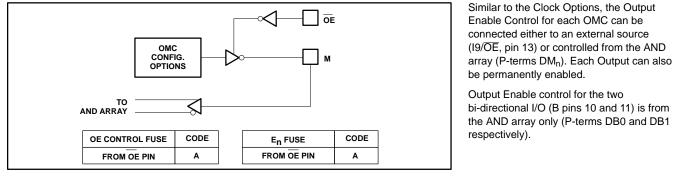

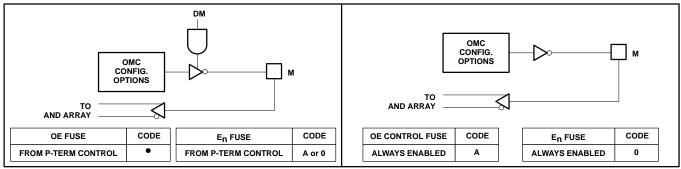

Sophisticated control functions support individual OE control and Reset functions from the AND array. OE control is also available from the 19/OE pin. Register Preset and Load functions are controlled from the AND array, in 2 banks of 4 for OMCs M1 – M8. Output Macro Cells M0 and M9 have individual Preset and Load Control terms.

Output Polarity for the combinatorial I/O paths is configurable via 12 programmable EX-OR gates. The output of each register can be configured as inverting (active Low) or non-inverting (active High) via manipulation of the logic equations.

The output of each buried register can also be configured as inverting or non-inverting via the input buffer which feeds back to the AND array.

PLC42VA12

## **OUTPUT MACRO CELL PROGRAMMABLE OPTIONS**

## ARCHITECTURAL OPTIONS

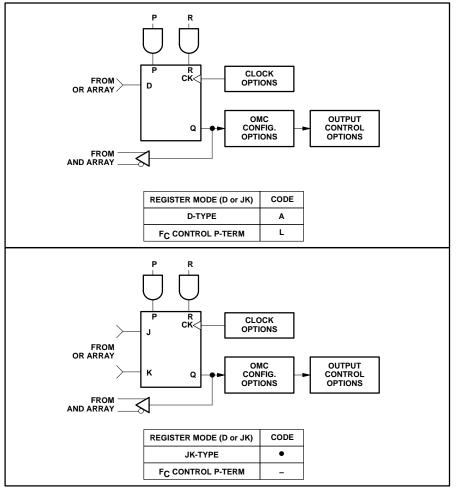

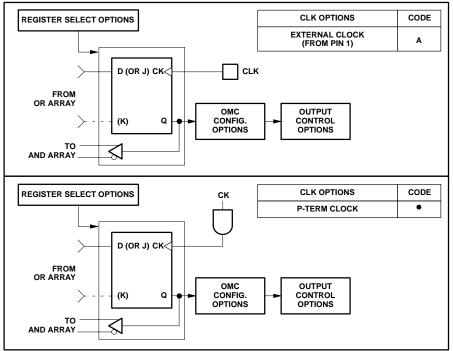

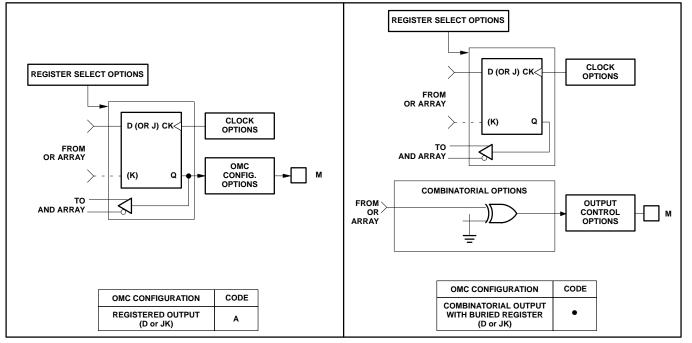

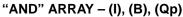

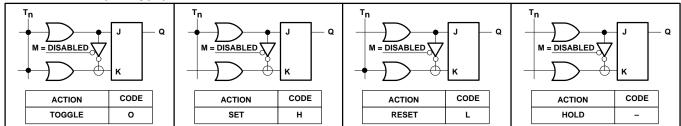

### **REGISTER SELECT OPTIONS**

Notes on page 87.

### **OMC Programmable Options**

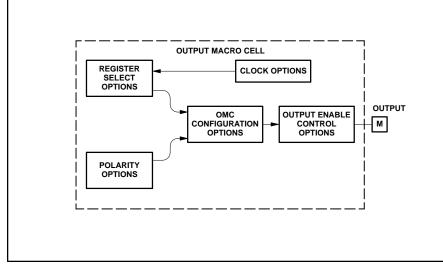

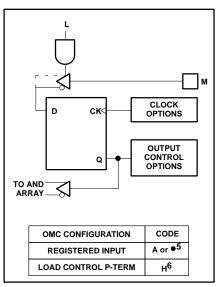

For purposes of programming, the Output Macro Cell should be considered to be partitioned into five separate blocks. As shown in the drawing titled "Output Macro Cell Programmable Options", the programmable blocks are: Register Select Options, Polarity Options, Clock Options, OMC Configuration Options and Output Enable Control Options.

There is one programmable location associated with each block except the Output Enable Control block which has two programmable fuse locations per OMC.

The following drawings detail the options associated with each programmable block. The associated programming codes are also included. The table titled "Output Macro Cell Configurations" (page 87) lists all the possible combinations of the five programmable options.

### **Register Select Options**

Each OMC Register can be configured either as a dedicated D-type or a J-K flip-flop. The Flip-Flop Control term, Fc, provides the option to control each Register dynamically—switching from D-type to J-K type, based on the Fc control signal.

Register Preset and Reset are controlled from the AND array. Each OMC has an individual Reset Control term (RMn). The Register Preset function is controlled in two banks of 4 for OMCs M1 – M3 and M4 – M8 (via the control terms PA and PB). OMCs M0 and M9 have individual control terms (PM0 and PM9 respectively).

## PLC42VA12

### **REGISTER SELECT OPTIONS** (Continued)

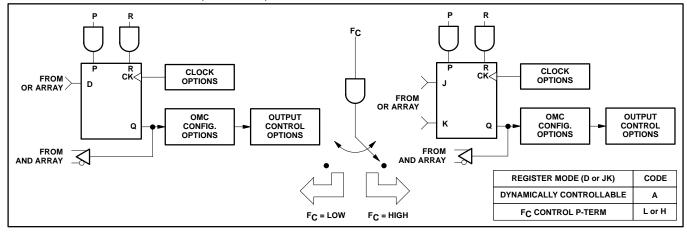

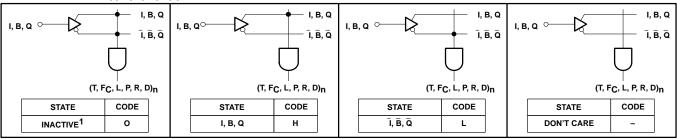

## POLARITY OPTIONS (for Combinatorial I/O Configurations Only<sup>1</sup>)

## **Polarity Options**

When an OMC is configured as a Combinatorial I/O with Buried Register, the polarity of the combinatorial path can be programmed as Active-High or Active-Low. A configurable EX-OR gate provides polarity control.

If an OMC is configured as a Registered Output, /Q is propagated to the output pin. Note that either Q or /Q can be fedback to the AND array by manipulating the feedback logic equations. (TRUE or COMPLEMENT).

## **CLOCK OPTIONS**

## **Clock Options**

In the unprogrammed state, all Output Macro Cell clock sources are connected to the External Clock pin ( $I_0$ /CLK pin 1). Each OMC can be individually programmed such that its P-term Clock (CK<sub>n</sub>) is enabled, thus disabling it from the External Clock and providing event-driven clocking capability.

This feature supports multiple state machines, clocked at several different rates, all on one chip, or the ability to collect large amounts of random logic, including 10 separately clocked flip-flops.

Notes on page 87.

## PLC42VA12

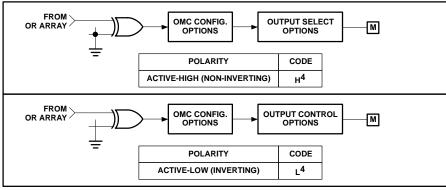

## OUTPUT MACRO CELL CONFIGURATION OPTIONS

Notes on page 87.

## **OMC Configuration Options**

Each OMC can be configured as a Registered Output with feedback, a Registered Input or a Combinatorial I/O with Buried Register. Dedicated Input and dedicated I/O configurations are also possible.

When the Combinatorial I/O option is selected, (the Register Bypass option), the Buried Register remains 100% functional, with its own inputs from the AND array and a separate feedback path. This unique feature is ideal for designing any type of state machine; synchronous Mealy-types that require both Buried and Output Registers, or asynchronous Mealy-types that require buried registers and combinatorial output functions. Both synchronous and asynchronous Moore-type state machines can also be easily accommodated with the flexible OMC structure. Note that an OMC can be configured as either a Combinatorial I/O (with Buried Register) or a Registered Output with feedback and it can still be used as a Registered Input. By disabling the outputs via any OE control function, the M pin can be used as an input. When the Load Control P-term is asserted HIGH, the register is preloaded from the M pin(s). When the L<sub>C</sub> P-term is Active-Low and the output is enabled, the OMC will again function as configured (either a combinatorial I/O or a registered output with feedback). This feature is suited for synchronizing input signals prior to commencing a state sequence.

PLC42VA12

**Output Enable Control Options**

### **OUTPUT CONTROL OPTIONS**

## COMPLEMENT ARRAY DETAIL

#### Notes on page 87.

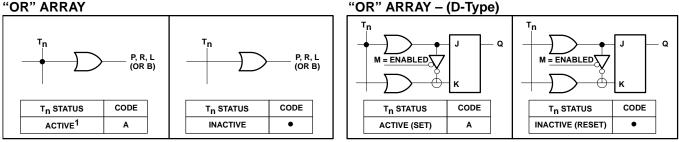

#### **Complement Array Detail**

The complement array is a special sequencer feature that is often used for detecting illegal states. It is also ideal for generating IF-THEN-ELSE logic statements with a minimum number of product terms.

The concept is deceptively simple. If you subscribe to the theory that the expressions (/A \* /B \* /C) and  $(\overline{A + B + C})$  are equivalent, you will begin to see the value of this single term NOR array.

The complement array is a single OR gate with inputs from the AND array. The output of the complement array is inverted and fedback to the AND array (NOR function). The output of the array will be LOW if any one or more of the AND terms connected to it are active (HIGH). If, however, all the connected terms are inactive (LOW), which is a classic unknown state, the output of the complement array will be HIGH.

Consider the product terms A, B and D that represent defined states. They are also connected to the input of the complement array. When the condition (not A and not B and not D) exists, the Complement Array will detect this and propagate an Active-High signal to the AND array. This signal can be connected to product term E, which could be used in turn to preset the state machine to known state. Without the complement array, one would have to generate product terms for all unknown or illegal states. With very complex state machines, such an approach can be prohibitive, both in terms of time and wasted resources.

PLC42VA12

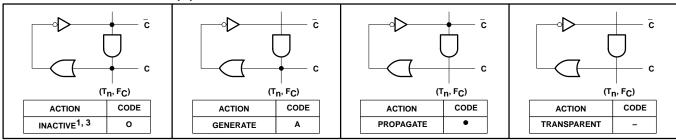

#### LOGIC PROGRAMMING

The PLC42VA12 is fully supported by industry standard (JEDEC compatible) PLD CAD tools, including Philips Semiconductors SNAP design software package. ABEL™ and CUPL™ design software packages also support the PLC42VA12 architecture.

All packages allow Boolean and state equation entry formats. SNAP, ABEL and CUPL also accept, as input, schematic capture format.

### LOGIC IMPLEMENTATION

PLC42VA12 logic designs can also be generated using the program table entry format, which is detailed on the following pages. This program table entry format is supported by SNAP only.

To implement the desired logic functions, the state of each logic variable from logic equations (I, B, O, P, etc.) is assigned a symbol. The symbols for TRUE, COMPLEMENT, INACTIVE, PRESET, etc., are defined below. Symbols for OMC

configuration have been previously defined in the Architectural Options section.

#### **PROGRAMMING AND** SOFTWARE SUPPORT

Refer to Section 9 (Development Software) and Section 10 (Third-party Programmer/ Software Support) of this data handbook for additional information.

### "COMPLEMENT" ARRAY - (C)

#### "OR" ARRAY – (J-K Type)

## "OR" ARRAY

Notes on page 87

ABEL is a trademark of Data I/O Corp. CUPL is a trademark of Logical Devices, Inc

## PLC42VA12

## LOGIC IMPLEMENTATION (Continued)

## **OUTPUT MACRO CELL CONFIGURATIONS**

|                                       | PROGRAMMING CODES       |                           |                       |               |  |  |  |

|---------------------------------------|-------------------------|---------------------------|-----------------------|---------------|--|--|--|

| OUTPUT MACRO CELL<br>CONFIGURATION    | REGISTER SELECT<br>FUSE | OMC CONFIGURATION<br>FUSE | POLARITY<br>FUSE      | CLOCK<br>FUSE |  |  |  |

| Combinatorial I/O with Buried D-type  |                         |                           |                       |               |  |  |  |

| External clock source                 | А                       | •                         | H or L                | А             |  |  |  |

| P-term clock source                   | А                       | •                         | H or L                | •             |  |  |  |

| Combinatorial I/O with Buried J-K ty  | pe register             |                           |                       |               |  |  |  |

| External clock source                 | •                       | •                         | H or L                | А             |  |  |  |

| P-term clock source                   | •                       | • •                       |                       | •             |  |  |  |

| Registered Output (D-type) with feed  | lback                   |                           |                       |               |  |  |  |

| External clock source                 | А                       | A                         | N/A                   | А             |  |  |  |

| P-term clock source                   | А                       | A                         | N/A                   | •             |  |  |  |

| Registered Output (J-K type) with fee | edback                  | •                         |                       |               |  |  |  |

| External clock source                 | •                       | A                         | N/A                   | А             |  |  |  |

| P-term clock source                   | •                       | A                         | N/A                   | •             |  |  |  |

| Registered Input (Clocked Preload)    | with feedback           |                           |                       |               |  |  |  |

| External clock source                 | А                       | A or ● <sup>5</sup>       | Optional <sup>5</sup> | А             |  |  |  |

| P-term clock source                   | А                       | A or ● <sup>5</sup>       | Optional <sup>5</sup> | •             |  |  |  |

|                                                     | OUTPUT CON      | TROL FUSES |                |

|-----------------------------------------------------|-----------------|------------|----------------|

| OUTPUT ENABLE CONTROL <sup>8</sup><br>CONFIGURATION | OE CONTROL FUSE | En FUSES   | CONTROL SIGNAL |

| OMC controlled by /OE pin                           | А               | А          |                |

| Output Enabled                                      |                 |            | Low            |

| Output Disabled                                     |                 |            | High           |

| OMC controlled by P-term                            | •               | A or 0     |                |

| Output Enabled                                      |                 |            | High           |

| Output Disabled                                     |                 |            | Low            |

| Output always Enabled                               | A               | 0          | Not Applicable |

NOTES:

1. This is the initial (unprogrammed) state of the device.

2. Any gate will be unconditionally inhibited if both the TRUE and COMPLEMENT fuses are left intact.

3. To prevent oscillations, this state is not allowed for Complement Array fuse pairs that are coupled to active product terms.

4. The OMC Configuration fuse must be programmed as Combinatorial I/O in order to make use of the Polarity Option.

5. Regardless of the programmed state of the OMC Configuration fuse, an OMC can be used as a Registered Input. Note that the Load Control P-term must be asserted Active-High.

6. Output must be disabled.

7. Program code definitions:

- $\tilde{A}$  = Active (unprogrammed fuse)

- $0, \bullet =$  Inactive (programmed fuse)

- = Don't Care (both TRUE and COMPLEMENT fuses unprogrammed)

- H = Active-High connection

- L = Active-Low connection

8. OE control for B0 and B1 (Pins 10 and 11) is from the AND array only.

## PLC42VA12

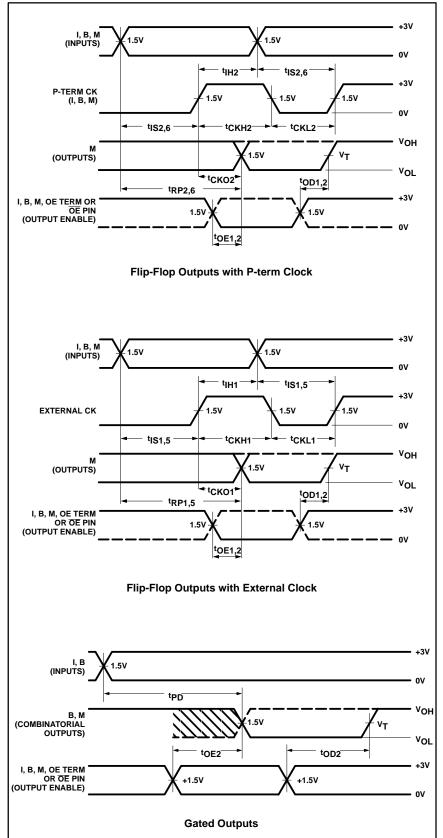

## TIMING DIAGRAMS

## TIMING DEFINITIONS

| SYMBOL            | PARAMETER                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>CK1</sub>  | Clock Frequency; External Clock                                                                                                                    |

| f <sub>CK2</sub>  | Clock Frequency; P-term Clock                                                                                                                      |

| t <sub>CKH1</sub> | Width of Input Clock Pulse;<br>External Clock                                                                                                      |

| t <sub>CKH2</sub> | Width of Input Clock Pulse;<br>P-term Clock                                                                                                        |

| t <sub>CKL1</sub> | Interval between Clock pulses;<br>External Clock                                                                                                   |

| t <sub>CKL2</sub> | Interval between Clock Pulses;<br>P-term Clock                                                                                                     |

| t <sub>CKO1</sub> | Delay between the Positive<br>Transition of External Clock and<br>when M Outputs become valid.                                                     |

| t <sub>CKO2</sub> | Delay between the Positive<br>Transition of P-term Clock and<br>when M Outputs become valid.                                                       |

| t <sub>RP1</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become Valid when using<br>External Clock.                                     |

| t <sub>RP2</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become Valid when using P-term<br>Clock.                                       |

| t <sub>RP3</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become Valid when using<br>Preload Inputs (from M pins) and<br>External Clock. |

| t <sub>RP4</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become valid when using<br>Preload inputs (from M pins) and<br>P-term Clock.   |

| t <sub>RP5</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become Valid when using Com-<br>plement Array and External<br>clock.           |

| t <sub>RP6</sub>  | Delay between beginning of Valid<br>Input and when the M outputs<br>become Valid when using Com-<br>plement Array and P-term Clock.                |

| f <sub>MAX1</sub> | Minimum guaranteed Operating<br>Frequency; Dedicated Clock                                                                                         |

| f <sub>MAX2</sub> | Minimum guaranteed Operating<br>Frequency; P-term Clock                                                                                            |

| f <sub>MAX3</sub> | Minimum guaranteed Operating<br>Frequency using Preload;<br>Dedicated Clock (M pin to M pin)                                                       |

| f <sub>MAX4</sub> | Minimum guaranteed Operating<br>Frequency using Preload; P-term<br>Clock (M pin to M pin)                                                          |

| f <sub>MAX5</sub> | Minimum guaranteed Operating<br>Frequency using Complement<br>Array; Dedicated Clock                                                               |

| f <sub>MAX6</sub> | Minimum Operating Frequency<br>using Complement Array; P-term<br>Clock                                                                             |

| t <sub>IH1</sub>  | Required delay between positive transition of External Clock and end of valid input data.                                                          |

## PLC42VA12

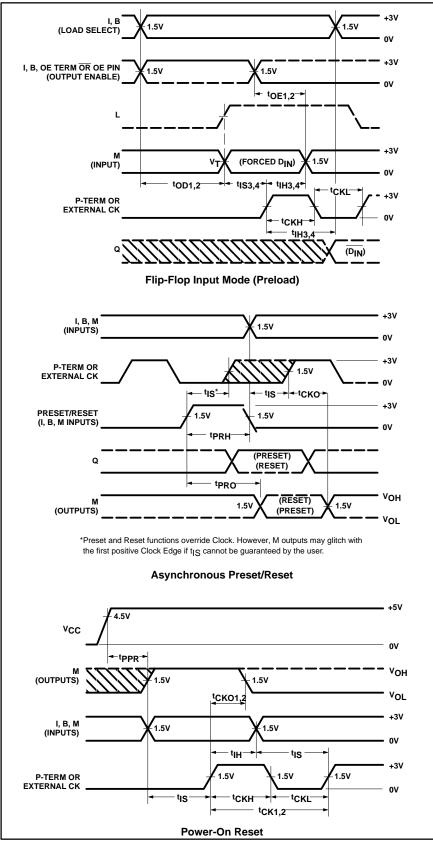

#### TIMING DIAGRAMS (Continued)

### TIMING DEFINITIONS (Continued)

| SYMBOL           | PARAMETER                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>IH2</sub> | Required delay between positive transition of P-term Clock and end of valid input data.                                                              |

| t <sub>IH3</sub> | Required delay between positive transition of External Clock and end of valid input data when using Preload Inputs (from M pins).                    |

| t <sub>IH4</sub> | Required delay between positive transition of P-term Clock and end of valid input data when using Preload Inputs (from M pins).                      |

| t <sub>IS1</sub> | Required delay between begin-<br>ning of valid input and positive<br>transition of External Clock.                                                   |

| t <sub>IS2</sub> | Required delay between begin-<br>ning of valid input and positive<br>transition of P-term Clock input.                                               |

| t <sub>IS3</sub> | Required delay between<br>beginning of valid Preload input<br>(from M pins) and positive<br>transition of External Clock.                            |

| t <sub>IS4</sub> | Required delay between<br>beginning of valid Preload input<br>(from M pins) and positive<br>transition of P-term Clock input.                        |

| t <sub>IS5</sub> | Required delay between<br>beginning of valid input through<br>Complement Array and positive<br>transition of External Clock.                         |

| t <sub>IS6</sub> | Required delay between<br>beginning of valid input through<br>Complement Array and positive<br>transition of P-term Clock input.                     |

| t <sub>OE1</sub> | Delay between beginning of<br>Output Enable signal (Low) from<br>/OE pin and when Outputs<br>become valid.                                           |

| t <sub>OE2</sub> | Delay between beginning of<br>Output Enable signal (High or<br>Low) from OE P-term and when<br>Outputs become valid.                                 |

| t <sub>OD1</sub> | Delay between beginning of<br>Output Enable signal (HIGH) from<br>/OE pin and when Outputs<br>become disabled.                                       |

| t <sub>OD2</sub> | Delay between beginning of<br>Output Enable signal (High or<br>Low) from OE P-term and when<br>Outputs become disabled.                              |

| t <sub>PD</sub>  | Delay between beginning of valid<br>input and when the Outputs be-<br>come valid (Combinatorial Path).                                               |

| t <sub>PRH</sub> | Width of Preset/Reset Pulse.                                                                                                                         |

| t <sub>PRO</sub> | Delay between beginning of valid<br>Preset/Reset Input and when the<br>registered Outputs become<br>Preset ("1") or Reset ("0").                     |

| t <sub>PPR</sub> | Delay between V <sub>CC</sub> (after<br>power-up) and when flip-flops<br>become Reset to "0". Note:<br>Signal at Output (M pin) will be<br>inverted. |

## PLC42VA12

## LOGIC FUNCTION

#### NOTE:

Similar logic functions are applicable for D mode flip-flops.

#### FLIP-FLOP TRUTH TABLE

| OE   | L <sub>n</sub> | CKn        | Pn | R <sub>n</sub> | J | Κ | Q | М    |

|------|----------------|------------|----|----------------|---|---|---|------|

| Н    |                |            |    |                |   |   |   | Hi-Z |

| L    | Х              | Х          | Х  | Х              | Х | Х | L | Н    |

| L    | Х              | Х          | Н  | L              | Х | Х | Н | L    |

| L    | Х              | Х          | L  | Н              | Х | Х | L | Н    |

| L    | L              | $\uparrow$ | L  | L              | L | L | Q | Q    |

| L    | L              | $\uparrow$ | L  | L              | L | Н | L | Н    |

| L    | L              | $\uparrow$ | L  | L              | Н | L | Н | L    |

| L    | L              | $\uparrow$ | L  | L              | Н | Н | Q | Q    |

| Н    | Н              | $\uparrow$ | L  | L              | L | Н | L | H*   |

| Н    | Н              | $\uparrow$ | L  | L              | Н | L | Н | L*   |

| +10V | Х              | $\uparrow$ | Х  | Х              | L | Н | L | H**  |

|      | х              | <b>↑</b>   | Х  | Х              | Н | L | н | L**  |

NOTES:

- 1. Positive Logic:  $\begin{array}{l} J \text{-}K = T_0 \text{ f}_{11}, T_2 + \dots + T_{31} \\ T_n = C \cdot (10 \cdot 11 \cdot 12 \dots) \cdot (Q0 \cdot Q1 \dots) \cdot \\ (B0 \cdot B1 \dots) \\ \uparrow \text{ denotes transition for Low to High level.} \end{array}$

- 2. 3. X = Don't care

- \* = Forced at M<sub>n</sub> pin for loading the J-K 4 flip-flop in the Input mode. The load control term,  $L_{n}$  must be enabled (HIGH) and the p-terms that are connected to the associated flip-flop must be forced LOW (disabled) during Preload.

- 5. At P = R = H, Q = H. The final state of Q depends on which is released first.

- \*\* = Forced at F<sub>n</sub> pin to load J/K flip-flop (Diagnostic mode).

#### PLC42VA12 UNPROGRAMMED STATE

A factory shipped unprogrammed device is configured such that all cells are in a conductive state.

#### The following are:

ACTIVE:

OR array logic terms

- Output Macro Cells M1 M8;

- D-type registered outputs (D = 0)

- External clock path

- Inputs: B0, B1, M0, M9

#### INACTIVE:

- AND array logic and control terms (except flip-flop mode control term, F<sub>C</sub>)

- Bidirectional I/O (B0, B1);

- · Inputs are active. Outputs are 3-Stated via the OE P-terms, D0 and D1.

- D-type registers (D = 0).

- Output Macro Cells M0 and M9;

- Bidirectional I/O, 3-Stated via the OE P-terms, DM0 and DM9. The inputs are active.

- P-term clocks

- Complement Array

- J-K Flip-Flop mode

### **PROGRAMMING AND** SOFTWARE SUPPORT

Refer to Section 9 (Development Software) and Section 10 (Third-party Programmer/ Software Support) in this data handbook for additional information.

#### ERASURE CHARACTERISTICS (For Quartz Window Packages Only)

The erasure characteristics of the PLC42VA12 devices are such that erasure begins to occur upon exposure to light with wavelength shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000 - 4000Å range. Data shows that constant exposure to room level fluorescent lighting could erase a typical PLC42VA12 in approximately three years, while it would take approximately one week to cause erasure when exposed to direct sunlight. If the PLC42VA12 is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure for the PLC42VA12 is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity × exposure time) for erasure should be a minimum of 15Wsec/cm<sup>2</sup>. The erasure time with this dosage is approximately 30 to 35 minutes using an ultraviolet lamp with a 12,000µW/cm<sup>2</sup> power rating. The device should be placed within one inch of the lamp tubes during erasure. The maximum integrated dose a CMOS EPLD can be exposed to without damage is 7258Wsec/cm<sup>2</sup> (1 week @ 12000µW/cm<sup>2</sup>). Exposure of these CMOS EPLDs to high intensity UV light for longer periods may cause permanent damage.

The maximum number of guaranteed erase/write cycles is 50. Data retentions exceeds 20 years.

October 22, 1993

## PROGRAM TABLE

Product specification

## PLC42VA12

## SNAP RESOURCE SUMMARY DESIGNATIONS